# ANALYSIS AND DESIGN OF SINGLE-PHASE GRID-CONNECTED BATTERY INVERTER USING DUAL ACTIVE BRIDGE DC-DC CONVERTER

A Thesis Submitted to the Graduate School of Naresuan University

in Partial Fulfillment of the Requirements

for the Doctor of Philosophy in Renewable Energy

2023

Copyright by Naresuan University

# ANALYSIS AND DESIGN OF SINGLE-PHASE GRID-CONNECTED BATTERY INVERTER USING DUAL ACTIVE BRIDGE DC-DC CONVERTER

A Thesis Submitted to the Graduate School of Naresuan University

in Partial Fulfillment of the Requirements

for the Doctor of Philosophy in Renewable Energy

2023

Copyright by Naresuan University

## Thesis entitled "Analysis and Design of Single-Phase Grid-Connected Battery Inverter Using Dual Active Bridge DC-DC converter"

#### By Akekachai Pannawan

has been approved by the Graduate School as partial fulfillment of the requirements for the Doctor of Philosophy in Renewable Energy of Naresuan University

#### **Oral Defense Committee**

| (Associate Professor Uthen Kamnarn, Ph.D.)   | Chair                                                        |

|----------------------------------------------|--------------------------------------------------------------|

| (Associate Professor Sakda Somkun, Ph.D.)    | Advisor                                                      |

| (Associate Professor Tawat Suriwong, Ph.D.)  | Internal Examiner                                            |

| (Assistant Professor Wisut Chamsa-ard, Ph.D  | Internal Examiner<br>.)                                      |

| (Assistant Professor Sahataya Thongsan, Ph.I | Internal Examiner D.)                                        |

|                                              | Approved                                                     |

|                                              | rofessor Krongkarn Chootip, Ph.D.) an of the Graduate School |

Title ANALYSIS AND DESIGN OF SINGLE-PHASE GRID-

CONNECTED BATTERY INVERTER USING DUAL

ACTIVE BRIDGE DC-DC CONVERTER

**Author** Akekachai Pannawan

Advisor Associate Professor Sakda Somkun, Ph.D.

**Academic Paper** Ph.D. Dissertation in Renewable Energy, Naresuan

University, 2023

**Keywords** Dual Active Bridge (DAB) DC-DC converter, LCL-filtered

Voltage Source Converter (VSC), Battery storage; DC-DC

converter; solar photovoltaic.

#### **ABSTRACT**

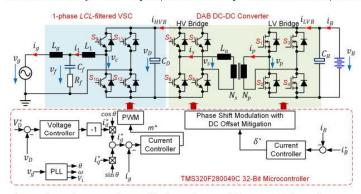

Combining residential energy storage with solar photovoltaic (PV) power generation within low-voltage distribution networks holds promise for attaining energy self-sufficiency. This research presents the design and implementation of such an approach using a 3-kW single-phase grid-connected battery inverter. The inverter pairs a 51.2-V lithium iron phosphate battery pack witha 220-V, 50-Hz grid. Its prototype design incorporates both an LCL-filtered voltage source converter (VSC) and a dual active bridge (DAB) DC-DC converter, both operating at a 20 kHzswitching frequency.

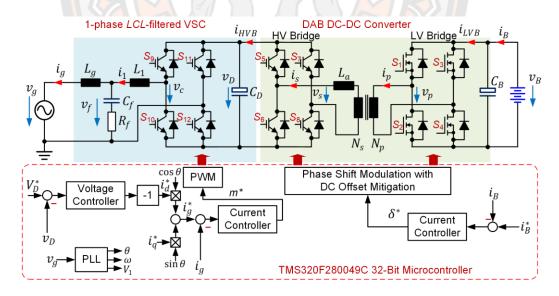

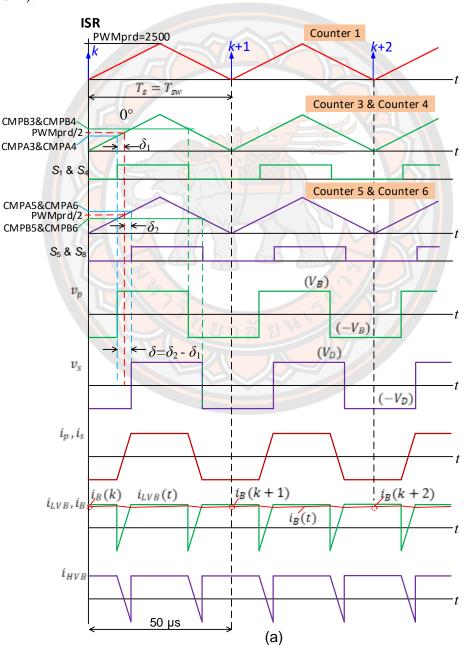

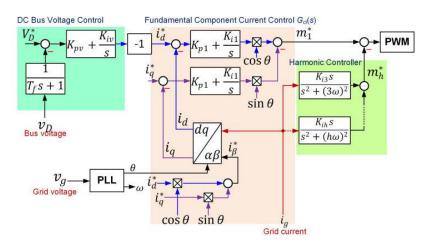

The VSC employs a swift DC bus voltage control strategy alongside a comprehensive approach to mitigate current harmonics. Similarly, the DAB DC-DC converter integrates a proportional-integral regulator to efficiently manage the average battery current, incorporating dynamic DC offset mitigation for the medium-frequency transformer's currents within its single-phase shift modulation scheme. The control strategies for both converters are executed on a 32-bit TMS320F280049C microcontroller within the same interrupt service routine, demonstrating the integration of control systems to enhance performance. This study introduces a synchronization technique aligning the switching signal generation of both converters with the sampling of analog signals for the control system, ensuring coordinated operations.

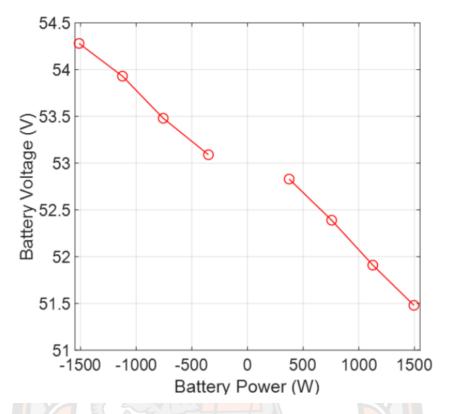

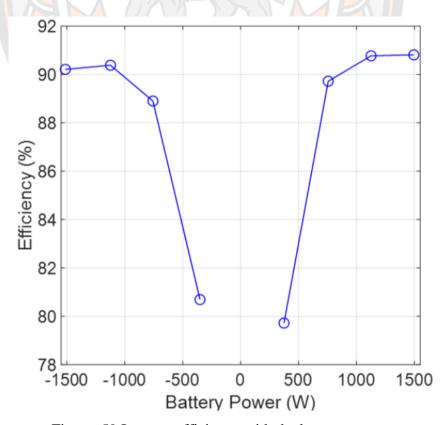

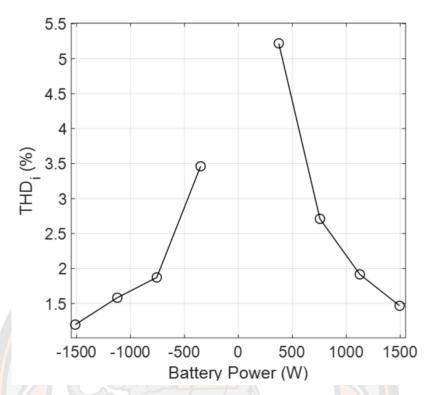

The prototype inverter exhibited exceptional performance, achieving an efficiency exceeding 90% and maintaining total harmonic distortion in the grid current below 1.5% at a battery power output of  $\pm 1.5$  kW, suggesting its potential to enhance grid stability and energy efficiency.

#### **ACKNOWLEDGEMENTS**

First and foremost, I extend my deepest gratitude to my thesis advisor, Associate Professor Dr. Sakda Somkun, for their unwavering support, insightful guidance, and invaluable advice throughout this research journey. Their expertise and encouragement were pivotal in shaping both the direction and success of this work.

I would also like to express my sincere thanks to the members of my thesis committee. Your constructive feedback, thoughtful criticisms, and engaging discussions have significantly contributed to refining my research. The depth and breadth of your expertise have enriched this work in countless ways.

I am immensely grateful to my lab mates and colleagues at Sepcon/SGtech for creating a stimulating and supportive work environment. Your camaraderie and collaborative spirit have made all the difference in my research experience. Working alongside such dedicated individuals has been both an honor and a pleasure.

To my friends and family, who have provided endless encouragement, understanding, and patience throughout the ups and downs of this academic pursuit: your belief in my abilities and unwavering support have been my strength during challenging times. I cannot thank you enough for standing by me every step of the way.

Finally, I want to express gratitude for the financial assistance provided by The Royal Golden Jubilee (RGJ) Ph.D. Program (Grant no. PHD02282560), which played a vital role in supporting my research and academic pursuits. This funding not only supported my studies but also created opportunities that were pivotal in finalizing this thesis.

This thesis stands as a testament to the collective effort and encouragement of all who have been part of this journey. Your contributions and support have been invaluable, and for that, I am forever grateful.

Akekachai Pannawan

## **TABLE OF CONTENTS**

| P                                                                                                               | age |

|-----------------------------------------------------------------------------------------------------------------|-----|

| ABSTRACT                                                                                                        | C   |

| ACKNOWLEDGEMENTS                                                                                                | Е   |

| TABLE OF CONTENTS                                                                                               | .F  |

| LIST OF TABLES                                                                                                  | Н   |

| LIST OF FIGURES                                                                                                 | . I |

| CHAPTER I INTRODUCTION                                                                                          | . 1 |

| Introduction                                                                                                    | . 1 |

| Background and Significance of the Study                                                                        | .3  |

| Objectives of the Study                                                                                         | .6  |

| Scope of the Study                                                                                              |     |

| Significance of the study                                                                                       |     |

| CHAPTER II LITERATURE REVIEW AND BASIC THEORY                                                                   | .8  |

| Literature review and basic theory                                                                              | .8  |

| The Dual Active Bridge DC-DC converter 1                                                                        | 4   |

| High-frequency magnetic materials and their application in power electronic converters                          | 8   |

| CHAPTER III MITIGATION OF GRID CURRRENT DITORTION OF SINGLE-<br>PHASE GRID-CONNECTED VOLTRAGE SOURCE CONVERTERS |     |

| Research Methodology                                                                                            | 22  |

| Grid current distortion due to voltage harmonics.                                                               | 23  |

| Grid current distortion due to the bus voltage control2                                                         | 27  |

| Analysis of Harmonic Mitigation Techniques3                                                                     | 80  |

| Harmonic Rejection Analysis of The Grid Current Control loop3                                                   | 80  |

| Unified Harmonic Mitigation Structure                                                                           | 32  |

| Proposed VSC Control scheme                                                                                     | 34  |

| Unbalanced synchronous reference frame control                                                                  | 34  |

| Proposed bus voltage control scheme                          | 37      |

|--------------------------------------------------------------|---------|

| Controller Design and Harmonic Rejection Analysis            | 42      |

| Grid Current Controller Design                               | 42      |

| Bus Voltage controller design                                | 44      |

| HARMONIC REJECTION ANALYSIS                                  | 46      |

| Simulation results                                           | 47      |

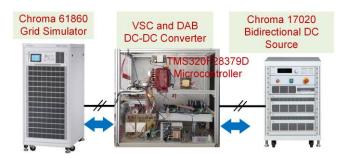

| Experimental setup                                           | 48      |

| EXPERIMENTAL RESULTS                                         | 49      |

| CHAPTER IV CONTROL OF DUAL ACTIVE BRIDGE DC-DC CONVE         | RTER.56 |

| Introduction                                                 | 56      |

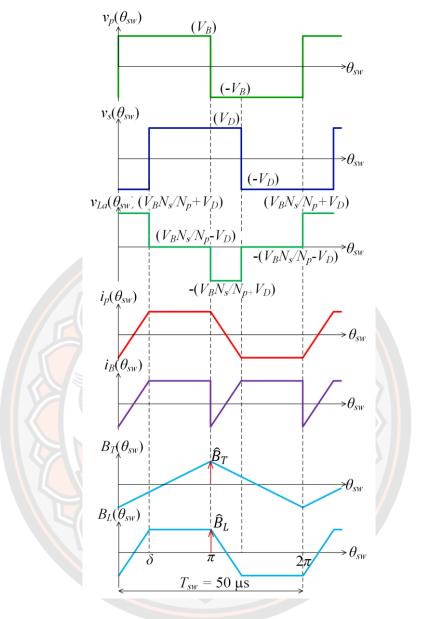

| Basic operation of the DAB DC-DC converter                   | 57      |

| Design of the transformer and series inductor                | 59      |

| Control system implementation of the DAB DC-DC converter     | 63      |

| Tuning of the battery current control loop                   | 66      |

| Experimental Validation                                      | 68      |

| Experimental results                                         | 69      |

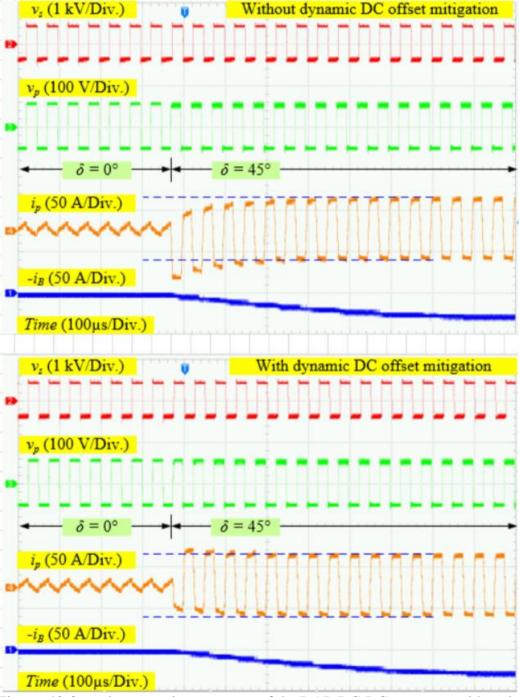

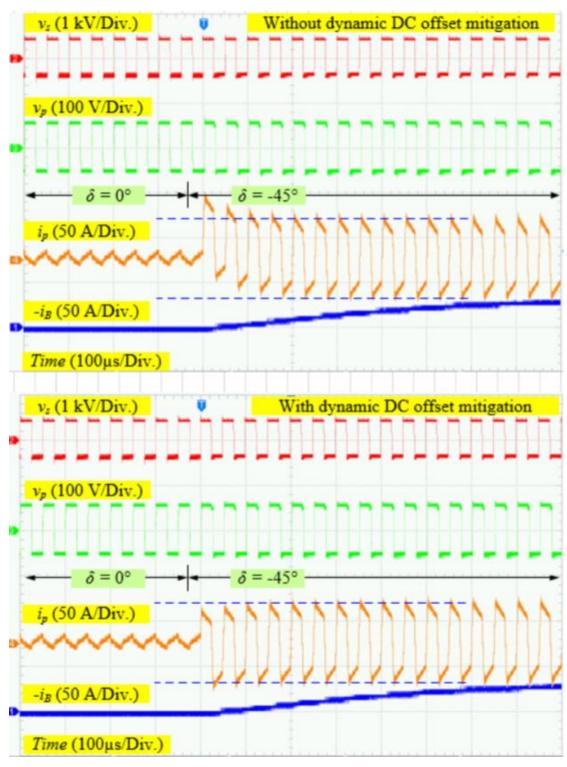

| Validation of the dynamic DC offset compensation scheme      | 69      |

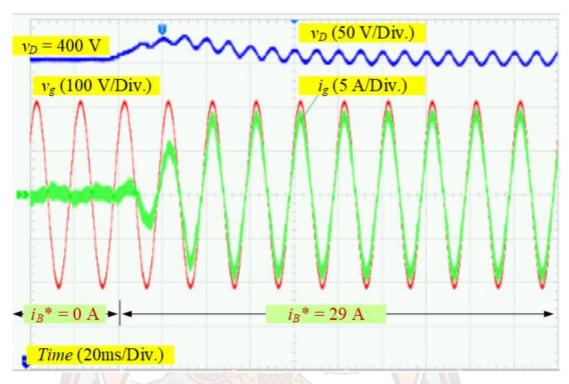

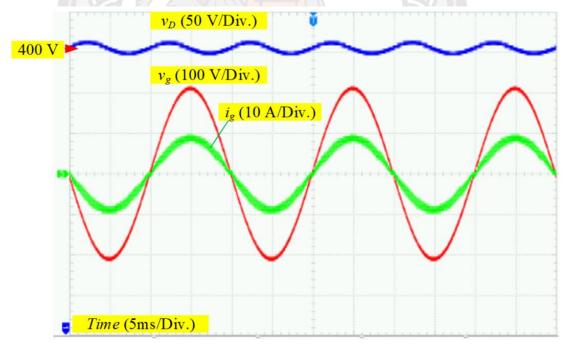

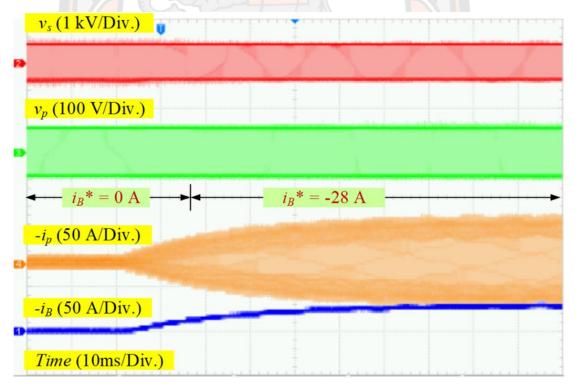

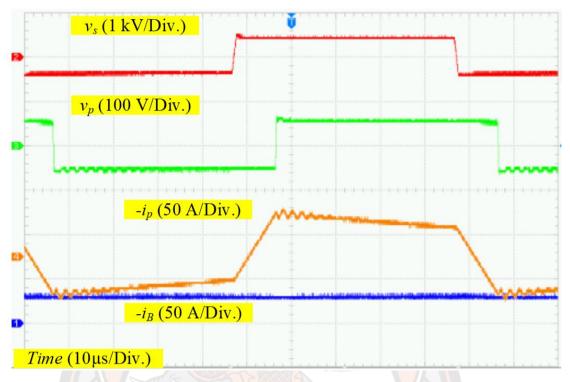

| Validation of the closed-loop control of the battery current | 72      |

| CHAPTER V DISCUSSION, CONCLUSION, AND FUTURE WORKS           | 80      |

| Discussion                                                   | 80      |

| Conclusion                                                   | 80      |

| Future Works                                                 | 82      |

| REFERENCES                                                   | 85      |

| APPENDIX                                                     | 92      |

| BIOGRAPHY                                                    | 128     |

## LIST OF TABLES

|                                                                               | Page    |

|-------------------------------------------------------------------------------|---------|

|                                                                               |         |

| Table 1 Harmonic Rejection Characteristics of the Grid Current Control Struct | ures 32 |

| Table 2 Parameters of the VSC and DAB DC-DC converter                         | 42      |

| Table 3 Specification of the battery inverter                                 | 60      |

| Table 4 Parameters of the battery inverter.                                   | 60      |

| Table 5 Parameters of the MF transformer and series inductor                  | 62      |

## **LIST OF FIGURES**

| Pa                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------|

| Figure 1 Dual active bridge DC-DC converter5                                                                           |

| Figure 2 DC coupling grid-connected PV-battery hybrid inverters: (a) Direct connection of the HV battery to the DC bus |

| Figure 3 AC coupling grid-connected PV-battery hybrid inverters                                                        |

| Figure 4 Single-phase LCL-filtered VSC and DAB DC-DC converter                                                         |

| Figure 5 Key waveform of the DAB converter in the SPS modulation strategy15                                            |

| Figure 6 Transferred power characteristic and the soft switching boundary conditions                                   |

| Figure 7 Pulse width modulation of the single-phase DAB DC-DC converter16                                              |

| Figure 8 Triple active bridge DC-DC converter (Zhao et al., 2008)17                                                    |

| Figure 9 Three-phase DAB DC-DC converter and its ideal waveforms                                                       |

| Figure 10 Six-leg three-phase DAB DC-DC converter (Waltrich et al., 2016)18                                            |

| Figure 11 B-H characteristics of soft magnetic materials                                                               |

| Figure 12 350-V 10-kVA and 20-kHz transformers for a DAB DC-Dc converter21                                             |

| Figure 13 research methodology for a study                                                                             |

| Figure 14 Single-phase LCL-filtered VSC and DAB DC-DC converter25                                                      |

| Figure 15 Single-phase LCL-filtered VSC25                                                                              |

| Figure 16 Equivalent bus voltage control block diagram                                                                 |

| Figure 17 Block diagram depicting grid current control in the stationary reference30                                   |

| Figure 18 Grid current control with parallel HC scheme                                                                 |

| Figure 19 Grid current control proposal featuring a zero-reference HC scheme34                                         |

| Figure 20 Stationary frame representation of the synchronous reference frame35                                         |

| Groupe 21 Unified structure of the unbalanced synchronous reference frame 36                                           |

| Figure | 22 Unbalanced synchronous reference frame control with the references in the         |

|--------|--------------------------------------------------------------------------------------|

| Figure | 23 Unbalanced synchronous reference frame control with the reference in the          |

| Figure | 24 Proposed DC bus voltage control system                                            |

| Figure | 25 Harmonic controller $Gcih(s)$ in the unbalanced synchronous reference 39          |

| Figure | 26 Traditional voltage regulation for a single-phase grid-connected VSC 40           |

| Figure | 27 Notch filter-based bus voltage control of the single-phase grid-connected41       |

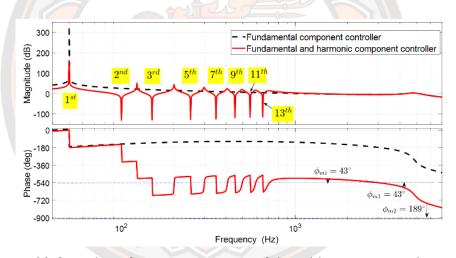

| Figure | 28 Open-loop frequency response of the grid current control systems44                |

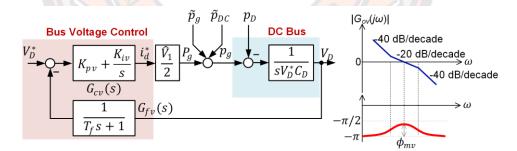

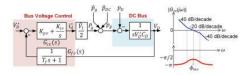

| Figure | 29 Equivalent bus voltage control block diagram and its open-loop frequency          |

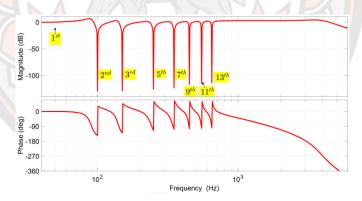

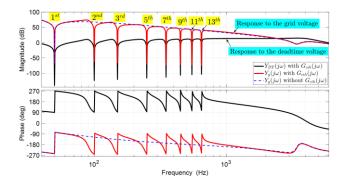

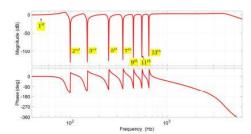

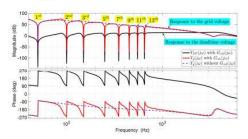

| Figure | 30 frequency response of the grid current to the reference current $Gcl(j\omega)$ 46 |

| Figure | 31 Frequency response of the grid current to the deadtime voltage $YDT(j\omega)$ 46  |

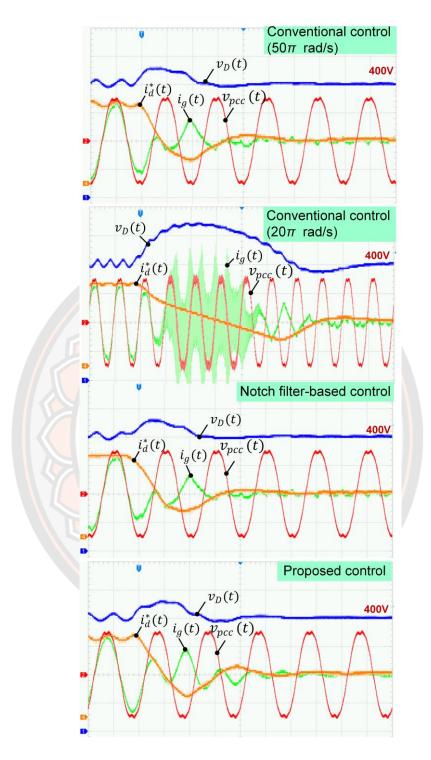

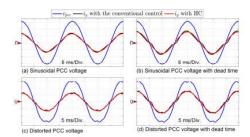

| Figure | 32 Simulation results of the VSC in the rectifier mode (vpcc(t): 10047               |

| Figure | 33 Simulation results of the VSC with the proposed bus voltage control in the        |

| Figure | 34 Experimental setup of the VSC                                                     |

| Figure | 35 Transient response of the VSC when the output power changing from51               |

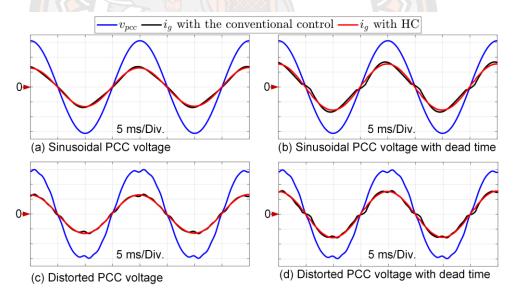

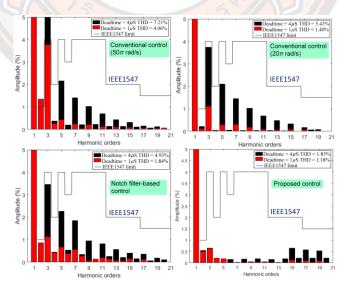

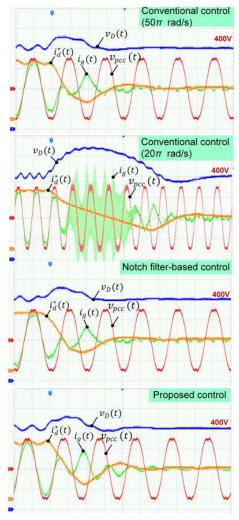

| Figure | 36 Steady state waveforms of the VSC with the output power of 2 kW under             |

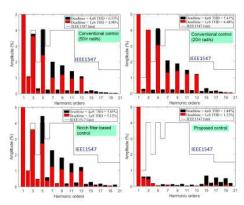

| Figure | 37 Harmonic components of the VSC current with the output power of 2 kW53            |

| •      | 38 Steady state waveforms of the VSC with the output power of 2 kW under             |

| Figure | 39 Harmonic components of the VSC current with the output power of 2 kW55            |

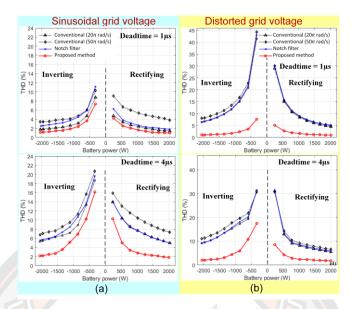

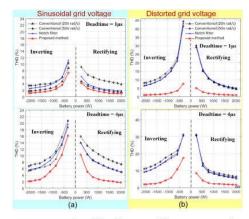

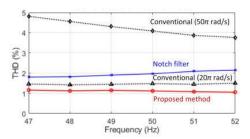

| Figure | 40 THDi values of the grid current with the output power under: (a) sinusoidal       |

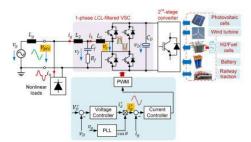

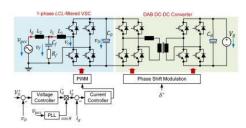

| •      | 41 Diagram and simplified control system of the inverter utilized in this study.     |

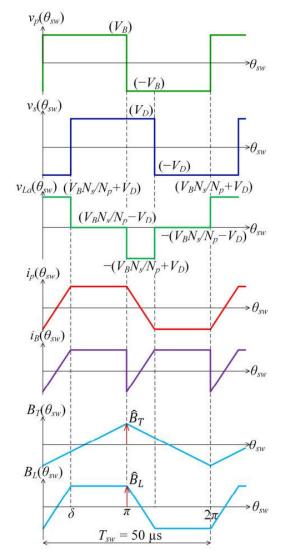

| Figure | 42 Voltage, current and flux density waveforms of the DAB DC-DC converter            |

|        | 59                                                                                   |

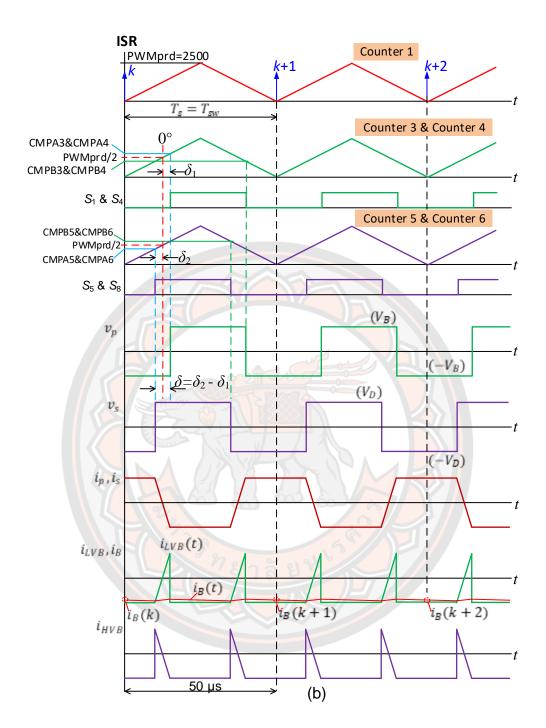

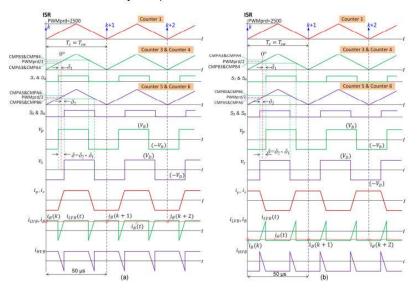

| Figure | 43 Steady state timing diagram for the DAB DC-DC converter: (a) For65                |  |  |

|--------|--------------------------------------------------------------------------------------|--|--|

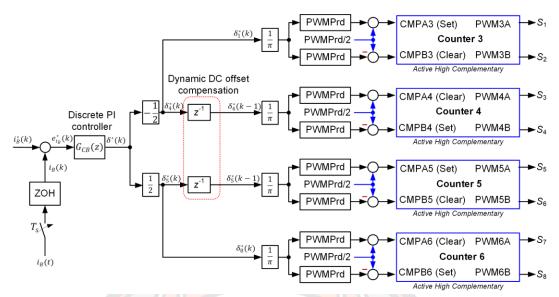

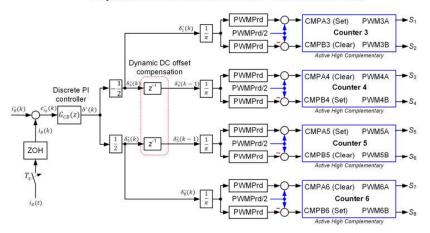

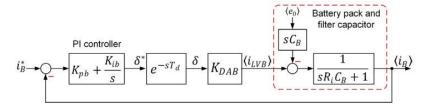

| Figure | 44 Implementation diagram of the battery current control loop of the DAB66           |  |  |

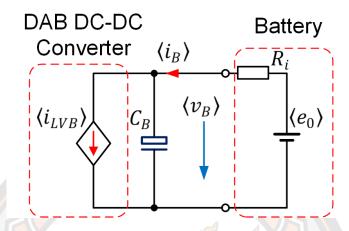

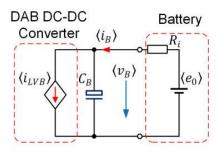

| Figure | 45 Equivalent circuit on the battery side                                            |  |  |

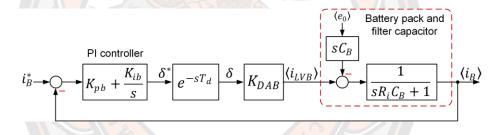

| Figure | 46 Block diagram of the control of battery current67                                 |  |  |

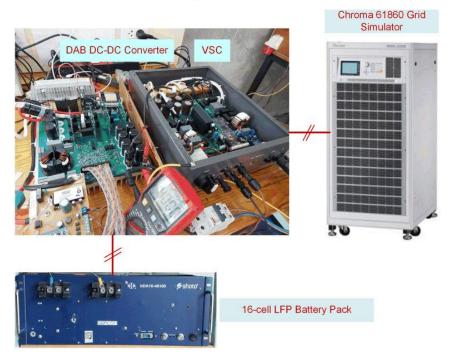

| Figure | 47 Experimental setup                                                                |  |  |

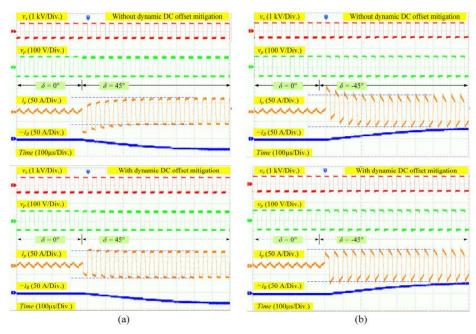

| Figure | 48 Open-loop transient response of the DAB DC-DC converter with and70                |  |  |

| Figure | 49 Open-loop transient response of the DAB DC-DC converter with and71                |  |  |

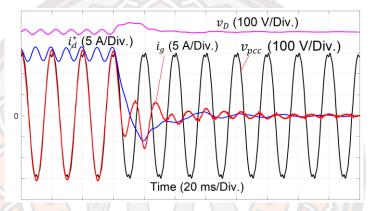

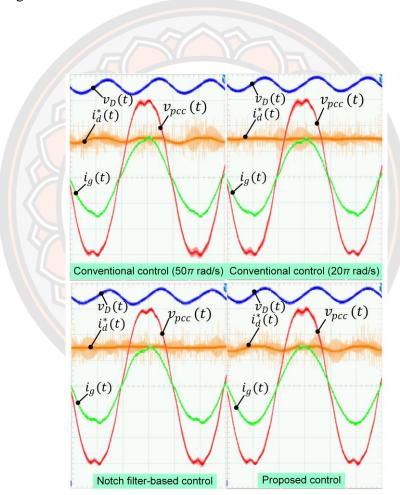

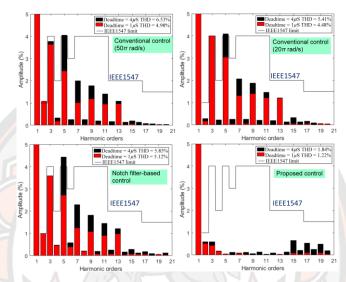

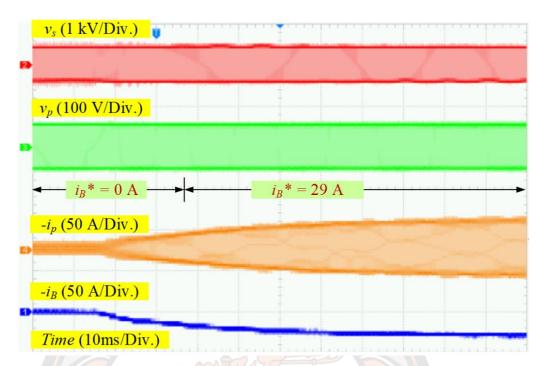

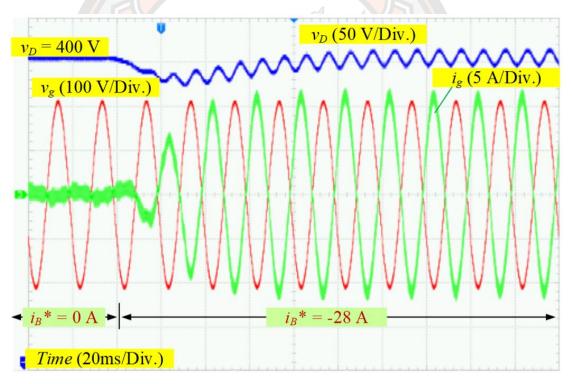

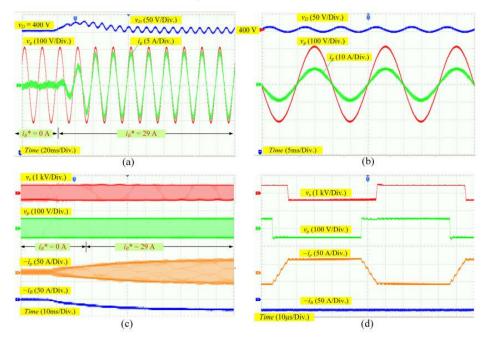

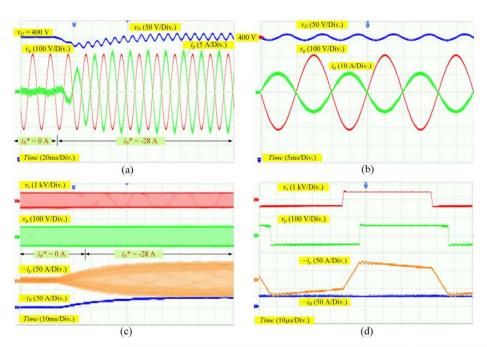

| Figure | 50 Transient response of the bus voltage $vD(t)$ , grid voltage $vg(t)$ ,73          |  |  |

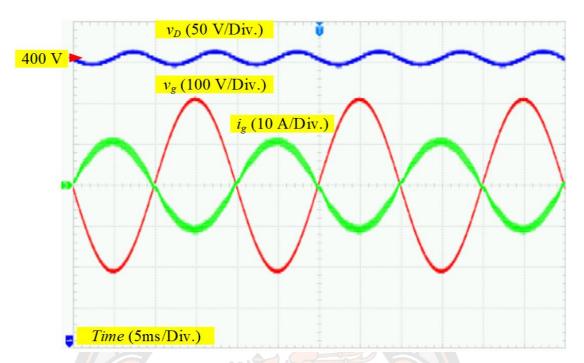

| Figure | 51 Steady state waveforms of the bus voltage $vD(t)$ , grid voltage $vg(t)$ , and 73 |  |  |

| •      | 52 Transient response of the primary and secondary voltages $vp(t)$ and $vs(t)$ ,    |  |  |

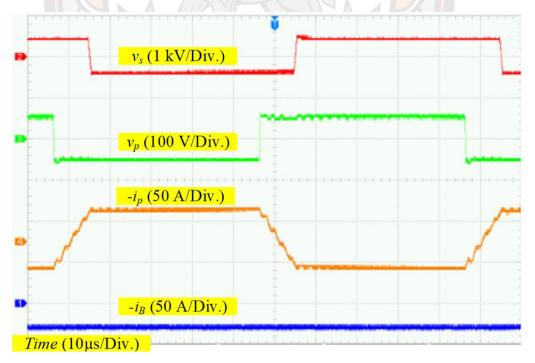

| -      | 53 Steady state waveforms of the primary and secondary voltages $vp(t)$ and          |  |  |

| Figure | 54 Transient response of the bus voltage $vD(t)$ , grid voltage $vg(t)$ , and grid75 |  |  |

| _      | 55 Steady state waveforms of the bus voltage $vD(t)$ , grid voltage $vg(t)$ , and    |  |  |

| Figure | 56 Transient response of the primary and secondary voltages $vp(t)$ and $vs(t)$      |  |  |

| Figure | 57 Steady state waveforms of the primary and secondary voltages $vp(t)$ and77        |  |  |

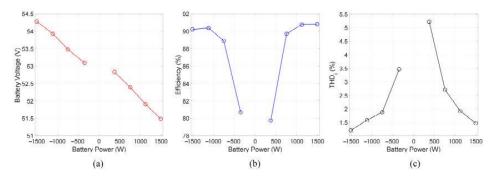

|        | 58 Battery voltage <i>VB</i> with the battery power                                  |  |  |

|        | 59 Inverter efficiency with the battery power                                        |  |  |

| Figure | 60 Total harmonic distortion of the grid current with the battery power 79           |  |  |

#### **CHAPTER I**

#### INTRODUCTION

#### Introduction

In the quest for the innovative solutions that facilitate the integration of the renewable energy to enhance power management in residential settings, the demand of compact, efficient, and reliable power conversion systems has led to the development of tailored designs for small-scale applications. This study focuses on two-stage, single-phase, grid-connected low-voltage (LV) battery inverter, which is specifically designed to meet the energy requirements of small residential applications. The central of this system is the dual-active bridge (DAB) DC-DC converter, which employs phase-shift modulation strategies to achieve bidirectional power flow and isolation for the LV battery pack. Complementing the DAB converter, the integration of LCL-filtered grid-connected voltage source converters (VSCs) enhance the system's capability to deliver clean and stable power from the grid to homes and vice versa. This introduction paves the way for the in-depth examination of the system's design, the operational efficiency, and the pivotal role, that plays in advancing residential power management and renewable energy adoption.

The Dual Active Bridge (DAB) DC-DC converter exemplifies the interest in power conversion technology, merging efficiency, reliability, and flexibility into a remarkably compact form factor, distinguished by its dual full-bridge architecture and the DAB converter enables bidirectional power flow. This capability makes it exceptionally suitable for the wide array of applications that demand a high efficiency and a precise power control across extensive ranges. Its operation at elevated switching frequencies facilitates the utilization of smaller magnetic components, therefore, diminishes both of dimensions and expenses, while maintaining its performance.

A standout feature of the DAB converter is its proficiency in achieving zerovoltage switching (ZVS) over a broad load range. This ability drastically cuts down not only switching losses, but also substantially boosting the system's overall efficiency. Coupled with its effective phase-shift modulation technique, the converter ensures a smooth power transfer control. This contributes to enhance the refined and stabled power output, in addition to epitomize technical finesse in managing energy flows.

The converter's adaptability is showcased in its broad spectrum of applications, ranging from electric vehicle charging infrastructures and the integration of renewable energy to enhancing grid stability and providing solutions for energy storage. Its efficiency in converting and regulating power between varying voltage levels plays a pivotal role in the seamless incorporation of renewable energy sources into the grid. This integration is crucial in steering the energy sector toward more sustainable practices.

Furthermore, the design of the DAB DC-DC converter incorporates sophisticated control strategies, which allow for dynamic adjustments in response to shifting loads and operational conditions. This flexibility guarantees sustained optimal performance and reliability, even amidst fluctuating power demands, encapsulating the essence of cutting-edge power electronics engineering.

Ultimately, the Dual Active Bridge DC-DC converter is a tribute to the advancements in power conversion technology. Its harmonious blend of efficiency, flexibility, and adaptability establish as a foundational element in the development of energy-efficient and environmentally friendly power systems. This marks a considerable stride towards achieving energy optimization and underscores a committed effort in environmental stewardship.

#### **Background and Significance of the Study**

The widespread adoption of renewable energy had transformed electrical generation and distribution systems into the distributed generation system (Lasseter, 2011). Generation sites were located based on the availability of renewable energy resources, e.g. wind, solar, small hydro, together with the conventional centralized power plants, e.g. natural gas, coal, nuclear etc. Energy storage devices such as batteries, hydrogen-fuel cells, pumped hydro storage systems, etc. were commonly used to overcome the intermittency such renewable energy sources (Boicea, 2014)[2]. Battery electric vehicles (BEVs) and plug-in hybrid electric vehicles (PHEVs) were also integrated into the electricity grid to utilize the cleaner renewable energy sources (Boulanger et al., 2011). In addition, energy stored in the BEVs and PHEVs could be used to support the grid when the demand was greater than the generation and reactive power injection for voltage regulation with the so-called vehicle to grid (V2G) operation (Falahi et al., 2013). The Smart grid system had been introduced to cope with the uncertainties of demand response and the variable generation of renewable energy sources (Kezunovic et al., 2012). One of the key characteristics of the smart grid was to accommodate of all power generation and storage options (Kezunovic et al., 2012). Thailand is also aware of the global context in the renewable generation and smart grid. According to the alternative energy development plan (Alternative Energy Development Plan: AEDP2018, 2018), Thailand had set a target that the share of renewable energy in the electricity production should increase from 9.87% in 2014 to 20.11% in 2036. Thailand smart grid development plan (2015 -2036) had been also launched to ensure energy security, to improve system reliability and power quality, and increase energy efficiency. Several smart grid pilot projects would be implemented throughout the country (Thailand Smart Grid Master Plan (2015-2036), 2015). EGAT, MEA and PEA are the key players in this smart grid plan.

Power electronic converters now play the vital role in the modern electric generation and distribution systems (Liserre et al., 2010)[8]. They are used to converse the AC variable voltage variable frequency (VVVF) sources/storages (wind, hydro, flywheel, etc.) and DC variable voltage (VV) sources/storages (photovoltaic, fuel cell, electrolyser, battery etc.) to AC constant voltage constant frequency

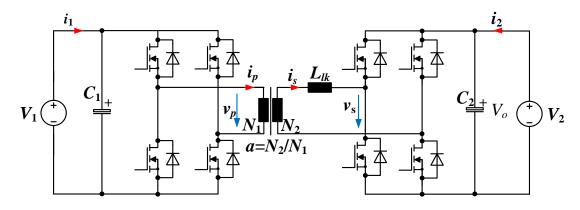

(CVCF), for delivering power to the utility grid. The most commonly used circuits are the voltage source AC-DC converters and DC-DC converters (De Doncker et al., 1991). Among these dual active bridge (DAB) DC-DC converters shown in Fig.1 are the most promising topology that gains attention from research communities. The basic principle is each bridge generates a square wave voltage to the transformer windings and the power transfer is controlled by the phase difference between the two voltage waveforms. The advantages of the DAB converters can be listed below (Kheraluwala et al., 1992):

- Bidirectional power transfer capability

- Zero voltage switching (ZVS) operation for efficiency enhancement

- Galvanic isolation through the high-frequency transformer

- High power density with the AC-link high-frequency voltage through the high-frequency transformer

- Easy voltage matching via the transformer turn ratio

- Fault current is limited with the auxiliary/leakage inductor (Harrye et al., 2015)[12].

The DAB DC-DC converters were widely used in solid state transformers (She et al., 2013)[13], on-board battery chargers of EVs and PHEVs (Xue et al., 2015), grid-connected battery converters (Inoue & Akagi, 2007a), railway traction systems (Baars et al., 2014), power conditioner circuits for fuel cells and photovoltaic modules with a high voltage step-up ratio (Cacciato et al., 2010), and uninterruptable power supplies (Zhao et al., 2013). Research on the DAB DC-DC converter could be mainly classified into three directions. First, control and modulation strategies had been developed so as to increase the efficiency and power factor of the high-frequency transformer (Jain & Ayyanar, 2011). The second approach was the application of wide-band gap semiconductor devices, mainly SiC IGBTs and SiC MOSFET (Zhao et al., 2014), as the power switches operating at a higher frequency in order to enhance the efficiency and power density. The third approach direction was the development of topology variants such as multi-input isolated DC-DC converter (Zhao et al., 2014), or three-phase DAB DC-DC converter (Waltrich et al., 2016) for high power applications with low ripple currents.

The high-frequency transformer and auxiliary inductor are the key components of the DAB DC-DC converter along with the two bridges. Ferrite materials were commonly used in transformers and inductors (Zhao et al., 2008). Iron-based nanocrystalline materials with a higher saturation induction and lower loss were also used as the transformer cores of the DAB converters (Inoue & Akagi, 2007a). Air-core inductors were commonly used in high power DAB DC-DC converters. Iron powder materials with higher saturation induction and lower permeability than the ferrite cores are also another choice for high-frequency inductors in power switching converters, which was found to be more compact than the ferrite cores (Rafiq et al., 2013). However, No direct comparison of high-frequency magnetic materials for the DAB converters has been made.

Thus, this project aims to explore the applications of high-frequency materials for the transformers and auxiliary inductors of the DAB DC-DC converters. As indicated in figure 1. Commercial and custom-made iron powder cores will be used to construct the auxiliary inductors. Commercial nanocrystalline materials will be selected for the transformers. Comparisons with the commonly used ferrites materials will be made. Lower losses and less core volumes lead to a higher efficiency and power density. This project is beneficial for the electronic, renewable energy and power transformer industry of Thailand. The knowledge obtained from this research can be transferred to the industry sector, therefore our domestic production of power converters can be competing with the imported products.

Figure 1 Dual active bridge DC-DC converter.

#### **Objectives of the Study**

- 1. To develop a Single-phase Grid-connected Voltage Source Converter (VSC) utilizing a full bridge topology.

- 2. To design and build a bidirectional isolated DC/DC converter based on a dual active bridge (DAB) configuration.

- 3. To develop and implement an advanced control strategy for a bidirectional isolated DC/DC converter using the Dual Active Bridge configuration, in addition to a single-phase grid-connected inverter employing a Voltage Source Converter (VSC).

#### Scope of the Study

- 1. Develop a Single-phase Grid-connected Voltage Source Converter (VSC) utilizing a full bridge topology. This involves the design and implementation of a converter capable of efficiently converting alternating current (AC) to direct current (DC) and vice versa, utilizing a full bridge configuration.

- 2. Design and construct a bidirectional isolated DC/DC converter based on a dual active bridge (DAB) configuration. The focus will be on creating a converter capable of bidirectional power transfer with isolation, using the DAB topology to achieve high efficiency and reliability.

- 3. Develop and implement an advanced control strategy for the bidirectional isolated DC/DC converter employing the Dual Active Bridge configuration. Additionally, integrate this control strategy with a single-phase grid-connected inverter utilizing a Voltage Source Converter (VSC). This involves developing sophisticated control algorithms to manage power flow and ensure stable operation in both the DC/DC converter and the grid-connected inverter.

#### Significance of the study

The study's significance is rooted in its contribution to the advancement of power conversion technologies and energy management strategies, which are essential for the integration of renewable energy sources into the power grid and the development of more efficient and sustainable energy systems. Below is a refined presentation of the study's significance:

- 1. The study introduces a Single-phase Grid-connected Voltage Source Converter(VSC), improving conversion efficiency. This is the key for integrating renewable energy, supporting energy storage, and enhancing electric vehicle charging, thereby promoting more sustainable energy use by reducing losses.

- 2. The development of a bidirectional isolated DC/DC converter based on a dual active bridge (DAB) enables safer, more efficient power transfer across voltage levels. The Essential of high-safety, low-noise applications such as renewable energy and electric vehicles, promotes wider adoption.

- 3. Implementing a control scheme for the isolated Dual Active Bridge (DAB)converter and a Voltage Source Converter (VSC), the study improves energy flow and grid stability with renewable sources. This supports reliable renewable use and smarter energy management, crucial for smart gride advancements.

#### **CHAPTER II**

#### LITERATURE REVIEW AND BASIC THEORY

#### Literature review and basic theory

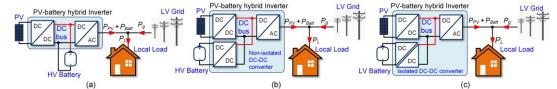

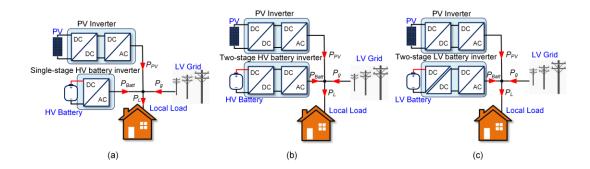

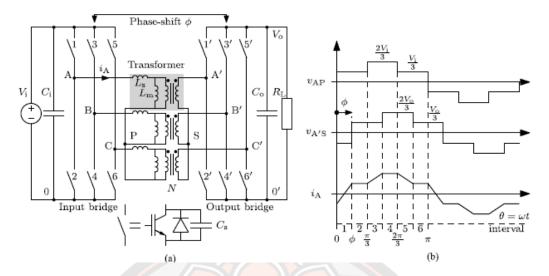

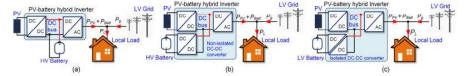

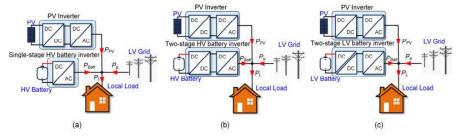

Integrating solar PV and battery storage into low-voltage distribution networks can be done using different configurations. One approach involves connecting the battery storage to the solar PV at the DC side of the grid inverter, as illustrated in Figure 2. Such configurations are known as DC-coupled solar PV-battery hybrid inverters. Typically, the voltage of the DC bus exceeds that of the PV, requiring the use of non-isolated boost DC-DC converters to match the PV string voltages with the DC bus voltage. The control system of the boost DC-DC converter incorporates maximum power point tracking (MPPT) to optimize performance. (Ahmed et al., 2022; Ko et al., 2020). A high voltage (HV) battery pack can be directly linked to the DC bus of the grid inverter, as depicted in Figure 2a (Galkin et al., 2021). For successful connection, the battery's voltage needs to exceed the grid inverter's minimum voltage requirement, which is the peak grid voltage for a single-phase system or the peak line-to-line voltage for a three-phase system. Additionally, an HV battery pack may be connected to the DC bus through a non-isolated DC-DC converter, as illustrated in Figure 2b. Usually, a bidirectional buck-boost DC-DC converter facilitates a broad battery voltage spectrum (200 V – 500 V), while ensuring the DC bus voltage remains above the grid-interfaced inverter's minimum threshold. Additionally, a battery pack necessitates an electronic battery management system (BMS) for the purpose of voltage equalization, overseeing, and safeguarding the galvanic cells. (Cao & Emadi, 2011). Hence, high-voltage battery storage solutions featuring intricate battery management systems (BMS) may be appropriate for select residential applications. On the other hand, for smaller homes (below 5 kW), lowvoltage battery storage (below 100 V) with a simpler and more cost-effective BMS presents a viable alternative, as shown in Figure 2c.(Galkin et al., 2021). The low-voltage (LV) battery pack connects to the DC bus via a bidirectional isolated DC-DC converter that uses a medium frequency (MF) transformer (20-150 kHz) to align the voltage of the LV battery pack with that of the DC bus. (Biao et al., 2014; Somkun et al., 2021). Battery storage can be incorporated into the low-voltage (LV) network using the AC coupling configurations depicted in Figure 3. Differing from the DC coupling arrangements depicted in Figure 2, which illustrates various examples of DC-coupled grid-connected photovoltaic-battery hybrid inverters, such as: (a) a high-voltage (HV) battery making a direct connection to the DC bus; (b) an HV battery connected to the DC bus via a non-isolated DC-DC converter; and (c) a low-voltage (LV) battery attached to the DC bus through an isolated DC-DC converter. The AC coupling strategy, on the other hand, incorporates a grid-interfaced inverter specifically for the battery systems and facilitates the flow of power between the solar photovoltaic system.  $(P_{PV})$ , battery power  $(P_{Batt})$ , load power  $(P_L)$ , and grid power  $(P_q)$  at the AC point of common coupling (PCC). However, AC coupling topologies are less efficient than their DC counterparts due to the additional conversion stage involved. (Lo Franco et al., 2021). However, AC coupling systems, as shown in Figure 3 which presents examples of AC-coupled grid-connected photovoltaic-battery hybrid inverters, including: (a) a single-stage high-voltage (HV) battery inverter; (b) a two-stage HV battery inverter; and (c) a two-stage low-voltage (LV) battery inverter, can be deployed with existing grid-connected PV inverters or independently of any PV inverters. They serve functions such as energy arbitrage or the reduction of peak load demand. (Galkin et al., 2021). Two-stage AC-coupled lowvoltage (LV) battery inverters, depicted in Figure 3c, are commonly employed in small residential environments with power needs under 5 kW. These power conversion stages and the battery pack can be integrated into a single, unified unit.("Duracell Energy Bank," 2024; "What to Expect for Powerwall 3," 2024).

Figure 2 DC coupling grid-connected PV-battery hybrid inverters: (a) Direct connection of the HV battery to the DC bus.

Figure 3 AC coupling grid-connected PV-battery hybrid inverters.

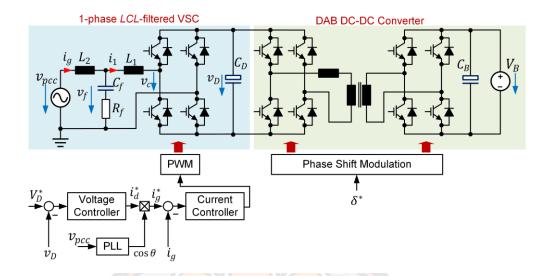

This research centers on a two-stage, single-phase, grid-connected low-voltage (LV) battery inverter designed for small-scale residential use. Typically, a dual-active bridge (DAB) DC-DC converter, utilizing phase-shift modulation techniques, serves as the bidirectional isolated DC-DC converter for the LV battery pack. For the gridinterfaced inverter, LCL-filtered grid-connected voltage source converters (VSC) are often chosen. Nonetheless, the efficiency may drop due to a limited zero-voltage switching (ZVS) range of the DAB DC-DC converter, especially when the voltage ratio across its terminals strays from its nominal value. (Kheraluwala et al., 1992). The efficiency of the dual-active bridge (DAB) DC-DC converter can be improved by integrating resonant networks with the medium frequency (MF) transformer, thereby expanding the range of zero-voltage switching (ZVS). (Jin et al., 2023; Zhou & Sun, 2022). The power transfer in the resonant dual-active bridge (DAB) DC-DC converter can be regulated by adjusting the switching frequency, a method that proves to be more complex than the fixed frequency operation seen in traditional DAB DC-DC converters. Additionally, the DAB DC-DC converter is prone to issues arising from an imbalance in the voltage-second applied to the medium frequency (MF) transformer, leading to a DC offset in the transformer's current. (Shu et al., 2019). To identify the DC offset component, the currents on both the primary and secondary sides of the transformer were measured ten times within a single switching period, and based on these measurements, the DC offset was corrected by adjusting the duty ratios of the two active bridges. This approach is effective in reducing both the dynamic and static components of the DC offset (Wang et al., 2018). For ease of implementation, the compensation for dynamic DC offset can be incorporated directly

into the modulation strategy by independently controlling the phase angle of each leg in the dual-active bridge (DAB) DC-DC converter. (Guzmán et al., 2021; Takagi & Fujita, 2018). The methods for compensating dynamic DC offset solely necessitate the use of delay elements.

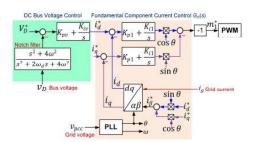

The bus voltage regulation was managed via the voltage source converter (VSC). An inherent double-frequency ripple present in the bus voltage has the potential to distort the waveform of the grid current. (Karimi-Ghartemani et al., 2013). Typically, a notch filter is utilized to prevent the double-frequency ripple component from entering the bus voltage control loop. This allows for an expansion of the loop's bandwidth with decreased bus capacitance, resulting in a nearly sinusoidal grid current waveform. (Somkun et al., 2023; Taghizadeh et al., 2019). Nevertheless, the presence of low-frequency harmonic components in the grid voltage and at the VSC terminal, arising from the dead time effect, could still lead to distortion in the grid current waveform. In a recent development, have implemented a comprehensive strategy for mitigating current harmonics in grid-connected voltage source converters (VSCs). This technique ensures that the grid current remains closely sinusoidal by rapidly controlling the bus voltage and eliminating harmonic components caused by grid fluctuations and the VSC's suboptimal switching.

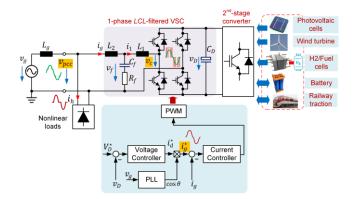

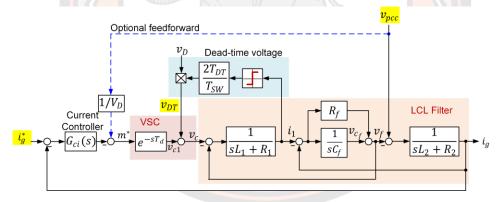

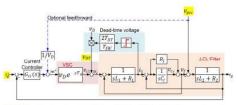

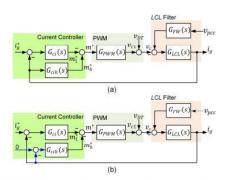

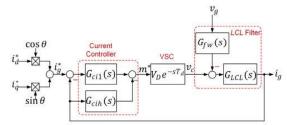

Single-phase voltage source converters (VSCs) have been extensively utilized in various applications such as integrating renewable energy sources into the grid (Karimi-Ghartemani et al., 2013; Li et al., 2017; Nguyen et al., 2017; Wang & Cai, 2010), battery storage systems (G. Liu et al., 2020), railway traction systems (Y. Liu et al., 2020), and as on-board battery chargers for plug-in vehicles(Nguyen et al., 2018; Taghizadeh et al., 2019). Figure 4 illustrates a common use case for the VSC, in which the DC bus voltage  $v_D(t)$  is typically connected to either a DC-DC converter or a three-phase VSC. The control strategy for these VSCs often involves a cascaded layout featuring an external loop for DC bus voltage control and an internal loop for managing the grid current. The primary goals of this control approach are to minimize fluctuations in the bus voltage, ensure a swift transient response to abrupt changes in bus power, and maintain low distortion in the grid current. However, challenges such as the distorted grid reference current  $i_a^*(t)$ , distorted voltage  $v_{pcc}(t)$  at the point of

common coupling (PCC), and the VSC terminal voltage  $v_c(t)$  affected by the deadtime voltage  $v_{DT}(t)$ , can introduce harmonic distortions into the grid current  $i_q(t)$ .

The double-frequency ripple within the DC bus voltage control loop leads to distortion in the reference current intended for the grid current control loop. Traditionally, this issue of the distorted current reference is mitigated by setting the control bandwidth of the bus voltage to significantly lower than the ripple's double frequency, typically around 10 Hz (Karimi-Ghartemani et al., 2013). Therefore, to curb significant transient fluctuations in the bus voltage, large aluminum electrolytic capacitors are employed. Furthermore, active ripple cancellation circuits (Mellincovsky et al., 2018; Zhong et al., 2016) separate the pulsating power from the average power, leading to reduced bus capacitance and enhanced control loop bandwidth. Nonetheless, these methods necessitate the use of extra semiconductor switches, more passive components, and complex control strategies.

Allowing for some degree of ripple voltage can lead to a reduction in bus capacitance (Strajnikov & Kuperman, 2022). Consequently, widening the bandwidth of the bus voltage control loop contributes to diminishing transient voltage fluctuations. Additionally, distortion in the reference current is typically reduced by preventing the ripple voltage from entering the bus voltage control loop. The prevalent approach to achieve this has been the use of a notch filter, which effectively blocks the double-frequency ripple(Khajehoddin et al., 2013; Li et al., 2017; Taghizadeh et al., 2019; Vongkoon et al., 2019). Other strategies include adaptive bus voltage control (Merai et al., 2019), ripple voltage estimation (Somkun & Chunkag, 2016a; Taghizadeh et al., 2019), nonlinear observers (Vule & Kuperman, 2022), and synchronizing bus voltage sampling with the grid frequency (Eren et al., 2015). These methods facilitate the generation of a clean reference current alongside rapid DC bus voltage control.

Figure 4 Single-phase LCL-filtered VSC and DAB DC-DC converter

Harmonic voltages lead to distortion in the grid current at both the point of common coupling (PCC) and the VSC terminals, attributed to a dead time,  $T_{DT}$ , present in each leg of the VSC. (Somkun, 2021; Yang et al., 2018). Incorporating feedforward of the voltage at the point of common coupling (PCC) has been partly effective in reducing the distortion of the grid current (Somkun, 2021). Nevertheless, a DC offset in the voltage measurement resulted in the undesirable injection of a DC component into the grid (Guo et al., 2021). The influence of dead time is markedly nonlinear and varies according to the current direction in the VSC. Reducing the dead-time voltage is achievable by adjusting the duty ratio, which is computed using either an adaptive algorithm (Herran et al., 2013) or an immune algorithm(Jiaxin et al., 2015). The harmonic voltages originating from the point of common coupling (PCC) and those arising due to dead time acted as disturbances within the grid current control loop. These disturbances could be alleviated by implementing a grid current controller equipped with selective harmonic mitigation techniques. Effective solutions include multi-frequency synchronous reference frame controllers (Somkun, 2021), multi-frequency proportional-resonant controllers(Elkayam & Kuperman, 2019; Kumar et al., 2022; Somkun, 2021), and repetitive controllers (RC) as demonstrated by previous studies(Yang et al., 2018).

The presence of harmonic voltages resulted in grid current distortion at both the Point of Common Coupling (PCC) and the terminals of the Voltage Source Converter (VSC) as a consequence of a dead time( $T_{DT}$ ) in each VSC leg (Somkun, 2021; Yang et al., 2018). Employing feedforward of the PCC voltage helped alleviate some of the distortion in the grid current (Somkun, 2021). Nevertheless, the presence

of a DC offset in voltage measurement led to an unwanted injection of a DC component into the grid (Guo et al., 2021). The impact of dead-time exhibited a highly nonlinear behavior, contingent upon the direction of VSC current. Mitigation of dead-time voltage could be achieved through adjustment of the compensated duty ratio, determined either via an adaptive algorithm (Herran et al., 2013) or an immune algorithm (Jiaxin et al., 2015). Both PCC and dead-time harmonic voltages represent disturbances within the grid current control loop, which can be addressed through the utilization of a grid current controller equipped with selective harmonic mitigation techniques. Effective solutions include multi-frequency synchronous reference frame controllers (Somkun, 2021), multi-frequency proportional-resonant controllers (Elkayam & Kuperman, 2019; Kumar et al., 2022; Somkun, 2021), and repetitive controllers (RC), as demonstrated in prior studies (Yang et al., 2018).

#### The Dual Active Bridge DC-DC converter

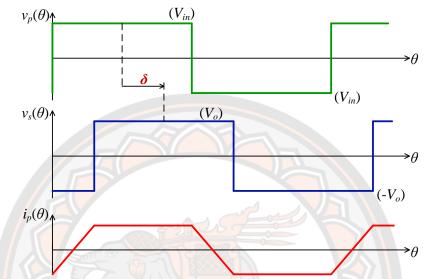

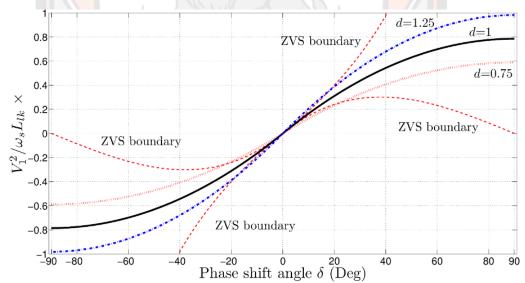

The DAB DC-DC converter was originally presented by De Doncker et at (De Doncker et al., 1991) as shown in Figure 1, where each bridge generates a square wave voltage to the transformer windings. The direction and magnitude of the transferred power was determined by the phase difference  $\delta$  between the primary and secondary voltages ( $v_p$  and  $v_s$ ) as follows (Kheraluwala et al., 1992).

$$P = \frac{N_1}{N_2} \frac{V_1 V_2}{\omega_{sw} L_{lk}} \delta \left( 1 - \frac{|\delta|}{\pi} \right) \tag{1}$$

where  $\omega_{sw}$  is the switching frequency and  $L_{lk}$  is the leakage inductance of the transformer. Normally, an auxiliary inductor is added to  $L_{lk}$  to limit the delivered maximum power of the circuit. Figure 5 illustrates the primary voltage  $v_p$ , secondary voltage  $v_s$ , and the primary current  $i_p$  operating in the single phase shift (SPS) modulation (Inoue & Akagi, 2007a; Kheraluwala et al., 1992), where the current reversion occurring after/before the reversion of the voltages allows the ZVS operation in the power switches. Figure 6 shows the normalized power transfer characteristic of the single-phase DAB DC-DC converter where

$$d = \frac{N_1}{N2} \frac{V_2}{V_1} \tag{2}$$

It is important to keep the voltage ratio between the two ports close to the transformer turn ratio (d = 1) so that the converter can be operated in the ZVS conditions for higher efficiency.

Figure 5 Key waveform of the DAB converter in the SPS modulation strategy.

Figure 6 Transferred power characteristic and the soft switching boundary conditions of the single-phase DAB DC-DC converter with the SPS strategy.

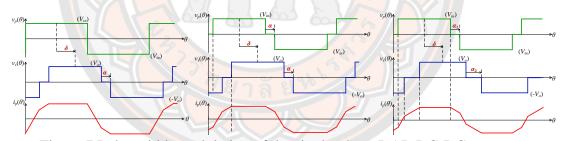

Apart from the narrow ZVS operation range, the SPS modulation scheme also faces pure transformer utilization due to the circulating current in the auxiliary inductor. Thus, the pulse width of the primary and/or secondary voltages are adjusted

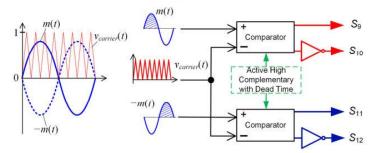

to accommodate a wider voltage regime by adding a phase shift between two phase legs of each bridge in order to increase the ZVS range and reduce the circulating current (Jain & Ayyanar, 2011). The pulse width modulation schemes of the singlephase DAB DC-DC converter can be summarized in Figure 7. The extended phase shift (EPS) method varies the pulse width only in one side of the transformer (Oggier et al., 2009), whereas the dual phase shift (DPS) and triple phase shift (TPS)(Zhao et al., 2012) schemes adjust the pulse width of both primary and secondary voltages. The difference between the DPS and TPS methods is that the TPS method varies the pulse width of the two voltage sides independently, while the pulse width of the two sides is identical for the DPS scheme. It is noted the phase angle  $\delta$  is also the main variable for the power transfer. In other words, the TPS is considered as the unified representation of the phase shift control for the single-phase DAB DC-DC converter. Although the TPS method gives the best performance among these modulation strategies, but it requires three control variables. Thus, the DPS scheme is considered to be optimal for a large-scale implementation. The SPS method is simple, and it is suitable for a narrow voltage range.

Figure 7 Pulse width modulation of the single-phase DAB DC-DC converter

(a) Extended phase shift scheme, (b) Dual phase shift scheme, (c) Triple phase shift scheme

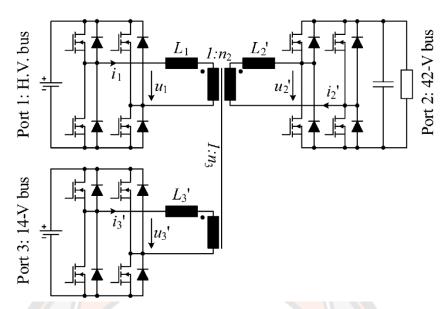

A third wining can be added to the transformer connected to another active bridge as shown in Figure 8 (Zhao et al., 2008). This topology is suitable for connecting a renewable energy source such as fuel cells or photovoltaic modules with the main DC bus and the third port is connected to an energy storage device such a battery. The advantages of this configuration are a compact structure due to the common use of a single transformer core, galvanic isolation, ease of voltage matching via the transformer turn ratios.

Figure 8 Triple active bridge DC-DC converter (Zhao et al., 2008)

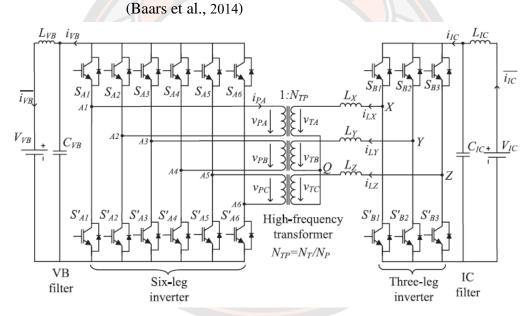

For high power applications, the DAB DC-DC converter could be implemented in the three-phase configuration as exhibited in Figure 9 (Baars et al., 2014)[32]. Each three-phase voltage source converter operates in the six-step mode and the power transferred is determined by the phase shift in each phase similar to the single-phase DAB converter. High power capability and lower component rating are the advantages of this topology. Moreover, the ripple current in each bridge is lower resulting in smaller filter capacitors. A six-leg inverter could be used instead of the three-leg inverter as shown in Figure 10 which increases control degrees (Waltrich et al., 2016). Moreover, the switches rating are reduced by half.

Figure 9 Three-phase DAB DC-DC converter and its ideal waveforms

Figure 10 Six-leg three-phase DAB DC-DC converter (Waltrich et al., 2016)

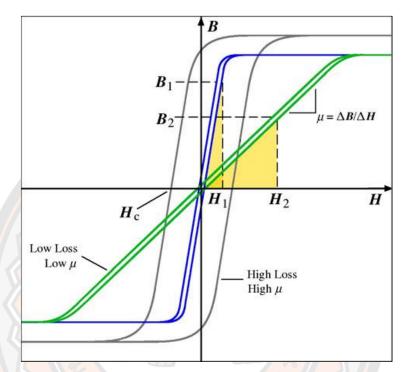

# High-frequency magnetic materials and their application in power electronic converters

High-frequency magnetic materials are used in the inductors of power electronic converters should exhibit low permeability so that a large amount of energy can be stored underneath the B-H curve as illustrated in Figure 11 (green curve). Moreover, the width of the B-H curve within a magnetizing period should be narrow to maintain low hysteresis loss. On the other hand, large permeability is desirable for

the high-frequency transformers so that large energy will be transferred across via the induced magnetic flux in the core (blue curve in Figure 11). For the electrical engineering point of view, large permeability results in lower magnetising current. Large saturation induction is preferred.

Figure 11 B-H characteristics of soft magnetic materials

Table 1 compares the typical high-frequency materials is used in power electronics converters. Ferrites are the most commonly applied materials, which are made up of iron oxide (Fe2O3) mixed with other metals such as manganese (Mn), Zinc (Zn) etc.. Ferrites in general have low Curie temperature. Thus, magnetic properties of ferrites vary with temperature significantly. For example, the saturation flux density of Epcos N87 MnZn material reduces from 0.49 T at 25°C to 0.39 T at 100°C. Ferrites have relatively high permeability. Cut cores with air gap are normally used to construct a high-frequency inductor. However, poor manufacturing techniques are greatly influence to cut core properties and can lead to higher loss (Leary et al., 2012).

Table 1 Summary of high-frequency soft magnetic materials

| Materials                    | Ferrites             | Nanocrystalline        | Powdered iron        |

|------------------------------|----------------------|------------------------|----------------------|

| Model                        | Epcos N87            | Vitroperm 500F         | Micro-metals 75μ     |

| Permeability, $\mu_i$        | 2,200                | 15,000                 | 75                   |

| $\hat{B}$ , T                | 0.49                 | 1.2                    | 0.6-1.3              |

| $P_{fe}$ , W/cm <sup>3</sup> | 228 at 0.2T<br>50kHz | 312 at 0.2 T<br>100kHz | 1032 at 0.2 T 10 kHz |

| Curie temp., °C              | 210                  | 600                    | 665                  |

Iron powder materials are the suitable alternatives for the high-frequency inductor cores (Mori et al., 2014; Rafiq et al., 2013). They are manufactured from an iron or an iron alloy powder, that's mixed or glued with an insulation material, then compressed, either to a ring, or a toroid shape. The distributed gap causes a low permeability, which is a function of powder size, spacing and chemical composition. Rafiq et al. (Rafiq et al., 2013)compared inductors constructed from ferrite and iron powder cores of a 60-kW bidirectional DC-DC converter and found that the iron powder materials gave a lighter weight design than the ferrites with an insignificant difference in the converter efficiency.

Nanocrystalline materials contain ultra-fine iron-based alloy crystals, typically 7-20  $\mu m$  in size. Their relative permeability is typically 20,000 and the saturation flux density is as high as 1.5 T. They are made into a form of thin ribbon with a thickness of 15-25  $\mu m$ , which yields a low eddy current. Their advantages over the ferrites are the saturation flux density up to 1.2 T and stable magnetic properties over a wide temperature range due to the Curie temperature up to 600°C. They are suitable for high-frequency transformers up to 150 kHz. Example applications of nanocrystalline materials in the DAB DC-DC converters were illustrated in (Inoue & Akagi, 2007a; Zhao et al., 2014) Figure 12 shows a 10-kVA 20-kHz transformer made from Hitachi FINEMENT toroid (Inoue & Akagi, 2007b).

Figure 12 350-V 10-kVA and 20-kHz transformers for a DAB DC-Dc converter

Using FINEMET nanocrystalline toroid from Hitachi metal

(Inoue & Akagi, 2007a)

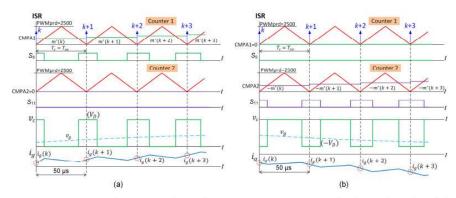

As previously noted, the control methodologies for the DAB DC-DC converter and grid-connected VSC have been extensively discussed. However, there is a lack of documentation on the microcontroller-based implementation techniques for these converters, including the generation of switching signals, interrupt requests, and analog signal sampling. Therefore, this study focuses on designing and implementing a single-phase grid-connected low-voltage battery inverter. This inverter comprises a DAB DC-DC converter and an LCL-filtered VSC, chosen for their consistent switching frequency application, which simplifies the control system's implementation. Both converters' control systems are executed in the same microcontroller within a shared interrupt service routine (ISR). The synchronous operation of generating switching signals for both the VSC and DAB DC-DC converter, as well as the analog signal sampling, is emphasized. Additionally, this research introduces a battery current control strategy, addressing dynamic DC offset mitigation of the MF transformer. The proposed inverter's experimental validation is also presented.

#### **CHAPTER III**

## MITIGATION OF GRID CURRRENT DITORTION OF SINGLE-PHASE GRID-CONNECTED VOLTRAGE SOURCE CONVERTERS

#### **Research Methodology**

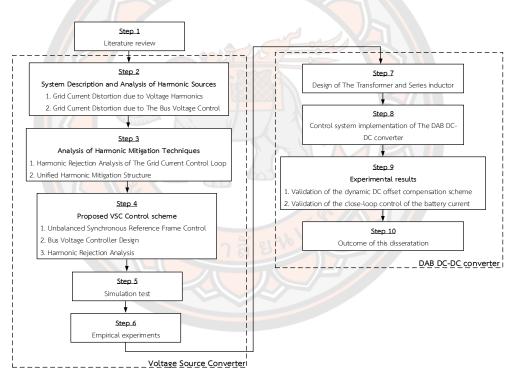

The flowchart illustrates the research methodology for a study focused on voltage source converters, detailing a systematic process followed by researchers from initial literature review to empirical experimentation.

Figure 13 research methodology for a study.

Figure 13 illustrates a method flowchart that encompasses two main sections: Voltage Source Converter (VSC) and Dual Active Bridge (DAB). The steps outlined in the flowchart include conducting a comprehensive literature review to understand the current state of voltage source converters and related technologies, analyzing voltage source conversion systems to identify sources of harmonic distortion, exploring techniques to reduce harmonic distortion within the converter, developing a

new control scheme for the VSC based on the analysis, simulating and validating the proposed control scheme in a virtual environment, conducting real-world empirical experiments to further verify and refine the control scheme, and finally, focusing on improving the control of the DC-DC converter section within the dual active bridge in subsequent steps (7-9). This flowchart provides a structured approach to investigating and enhancing voltage source converters, integrating theoretical insights with practical validation to advance understanding and performance.

#### Grid current distortion due to voltage harmonics.

The increasing penetration of non-linear loads and power electronic-based devices in electrical networks has accentuated the issue of voltage harmonics, a deviation from the ideal sinusoidal voltage waveform that can lead to various adverse effects on the power grid, including grid current distortion. This phenomenon has become a significant concern for both of utilities and end-users, as it directly impacts the efficiency, reliability, and quality of power delivery. The interaction between voltage harmonics and the grid introduces complex challenges that necessitate a comprehensive understanding and strategic mitigation approaches to ensure the stability and efficiency of the power system.

Voltage harmonics are primarily generated by non-linear loads, such as variable-speed drives, compact fluorescent lamps, and various types of power converters, which draw current in a non-sinusoidal manner. These harmonic currents, while injected into the power system, can cause voltage distortions due to the impedance of the network. The distortion in the voltage waveform, in turn, leads to current distortion in other parts of the grid, affecting devices and systems that are sensitive to waveform quality. The consequences of grid current distortion are numerous, ranging from heightened heat generation in electrical equipment to the improper functioning of protective devices and disruptions to communication lines. These issues can ultimately lead to reduced system efficiency and higher operational expenses.

The criticality of addressing grid current distortion due to voltage harmonics is underscored by the continuous evolution of power systems towards smart grids and the integration of renewable energy sources. As the energy landscape becomes increasingly complex, the resilience of the electrical grid to harmonic disturbances is paramount. This necessitates the adoption of innovative harmonic analysis, modeling, and mitigation techniques to preemptively address the issues posed by voltage harmonics.

This chapter aims to delve into the genesis of grid current distortion due to voltage harmonics, exploring its implications on power system operation and performance. By examining the mechanisms through which voltage harmonics induce current distortion, the paper seeks for highlight the interdependencies within the electrical grid that exacerbates this issue. Furthermore, it will review the existing strategies for harmonic mitigation and control, evaluating their effectiveness and exploring potential advancements in technology and regulation that could mitigate the impact of voltage harmonics on grid current distortion. Through this investigation, the paper endeavors to contribute to the ongoing dialogue on enhancing power quality and grid stability in the face of evolving electrical loads and generation paradigms.

In this investigation, a LCL-filtered grid-connected VSC depicted in Figure 14 and characterized by the parameters outlined in Table I is chosen. In accordance with the notation for grid current, the VSC operates in rectifier mode. The DC bus is linked to a DAB DC-DC converter serving as the second-stage converter to interface with a 400-V bidirectional DC source. This configuration finds utility in bidirectional onboard electric vehicle chargers and locomotive traction transformers. Control over the bidirectional bus power is achieved through phase shift modulation of the DAB DC-DC converter, manipulating the phase angle  $\delta$  between the primary and secondary voltages of the medium frequency transformer.

Figure 14 Single-phase LCL-filtered VSC and DAB DC-DC converter.

In Figure 15, the grid current control block diagram of the VSC in the stationary reference frame is presented. This study incorporates the distorted PCC voltage.

Figure 15 Single-phase LCL-filtered VSC

The distorted PCC voltage  $v_{pcc}(t)$  , as represented by

$$v_{pcc}(t) = \underbrace{\hat{V}_1 \cos \theta}_{v_1(t)} + \underbrace{\sum_{h=2}^n \hat{V}_h \cos(h\theta + \psi_h)}_{v_h(t)}$$

(3-1)

Here,  $\theta = \omega t$ ,  $\hat{V}_1$ , and  $\hat{V}_h$  represent the voltage amplitudes, and  $\psi_h$  signifies the phase angle of each harmonic component. The current controller  $G_{ci}(s)$  may take the form of a proportional-resonant (PR) regulator in the stationary reference frame or a PI

regulator in the synchronous reference frame. This controller ensures an infinite gain at the grid frequency  $\omega$  to attain zero steady-state error. The LCL filter governs the grid current  $i_g(t)$  in the following manner.

$$L_2 \frac{di_g(t)}{dt} + R_2 i_g(t) = v_{pcc}(t) - v_f(t)$$

(3-2)

$$v_f(t) = v_{cf}(t) + R_f(i_g(t) - i_1(t))$$

(3-3)

$$C_f \frac{dv_{cf}(t)}{dt} = i_g(t) - i_1(t)$$

(3-4)

$$L_{1} \frac{di_{1}(t)}{dt} + R_{1}i_{1}(t) = v_{f}(t) - \underbrace{(v_{c1}(t) + v_{DT}(t))}_{v_{c}(t)}$$

(3-5)

Disregarding the switching frequency elements, the ideal output voltage  $v_{c1}(t)$  of the VSC, as stated in equation (3-5), is regulated by the modulation signal $m^*(t)$  expressed as

$$v_{c1} \approx V_D m^*(t). \tag{3-6}$$

Equations (3-2) to (3-6) demonstrate the control of the grid current  $i_g(t)$  using the modulation signal  $m^*(t)$  with  $v_{pcc}(t)$  and  $v_{DT}(t)$  act as disturbances, leading to the introduction of low-order harmonics into the grid current. The dead-time voltage  $v_{DT}(t)$  in (3-5) can be approximated as

$$v_{DT}(t) \approx \frac{2T_{DT}}{T_{SW}} \operatorname{sign}(i_1(t)) v_D(t)$$

(3-7)

Here,  $T_{SW}$  represents the switching period. The term  $v_{DT}(t)$  can be compensated in  $m^*(t)$  using (3-7). However, for the LCL filter with the grid current feedback control used in this study, an additional current sensor is required for the dead time voltage compensation. A feedforward of  $v_{pcc}(t)$  helps alleviate grid current distortion to some extent (Somkun, 2021). Nevertheless, there might be a DC offset in voltage measurement, leading to the introduction of a DC component in the grid current (Guo et al., 2021).

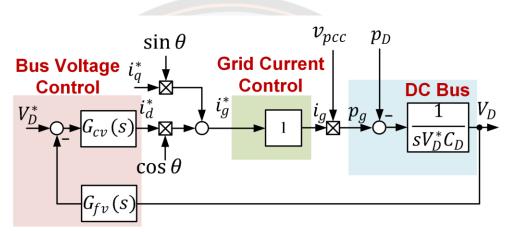

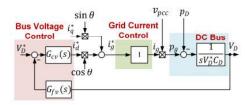

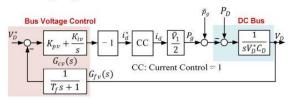

### Grid current distortion due to the bus voltage control

Figure 16 illustrates the simplified block diagram of the bus voltage control loop, where the grid current control loop is simplified to unity gain. The bus voltage  $v_D(t)$  undergoes filtering through the bus voltage filter  $G_{fv}(s)$  before being compared with the reference bus voltage  $V_D^*$  by the bus voltage controller  $G_{cv}(s)$ . The bus voltage filter may take the form of either a low-pass filter or a notch filter tuned at  $2\omega$

Figure 16 Equivalent bus voltage control block diagram.

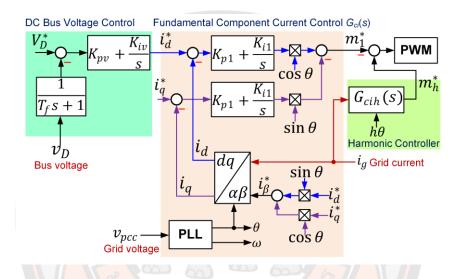

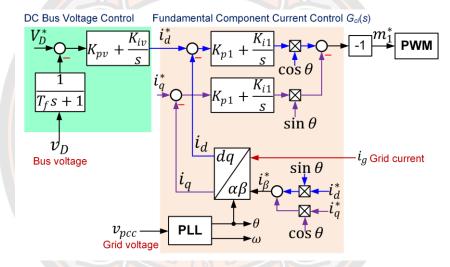

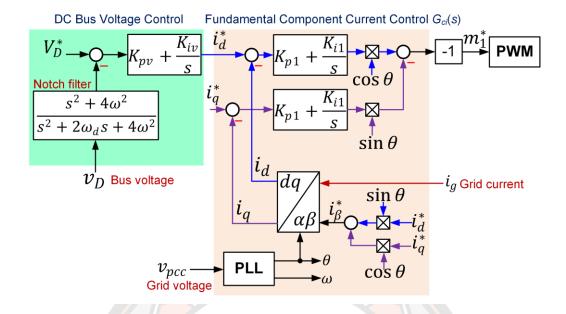

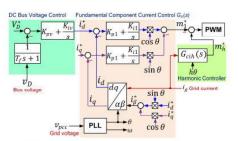

Typically, a Proportional-Integral (PI) controller is used as the bus voltage controller. This controller produces the reference current  $i_d^*$  indicating the necessary active power to be drawn from or injected into the grid. Additionally, the reference current  $i_q^*$  sets the reactive power. These reference currents,  $i_d^*$  and  $i_q^*$  are multiplied by  $\cos\theta$  and  $\sin\theta$  templates derived from a phase-locked loop (PLL). This multiplication yields the reference signa  $i_q^*$  for the inner current control loop.

In this analysis, let's assume that the grid current  $i_g(t)$  initially comprises a DC component  $I_{g0}$  and an AC fundamental component  $i_{g1}(t)$  The expression for the grid current  $i_g(t)$  is as follows:

$$i_g(t) = I_{g0} + \underbrace{\hat{I}_1 \cos(\theta + \phi_1)}_{i_{g1}(t)}$$

(3-8)

Here,  $\hat{l}_1$  and  $\phi_1$  represent the amplitude and phase angle of  $i_{g1}(t)$ . The presence of asymmetry in semiconductor properties, gate driver delays, and offset in

grid current measurement contribute to the DC component current  $I_{g0}$  (Zhang et al., 2019). The grid current  $i_{g1}(t)$  can be split into its components producing active and reactive power,  $i_d(t)$  and  $i_g(t)$ , expressed as:

$$i_{g1}(t) = \underbrace{\hat{l}_1 \cos \phi_1}_{i_d} \cos \theta - \underbrace{\hat{l}_1 \sin \phi_1}_{i_q} \sin \theta. \tag{3-9}$$

Using the fundamental component of the PCC voltage, the instantaneous grid power can be expressed as follows:

$$p_{g}(t) = v_{pcc}(t) \cdot i_{g}(t)$$

$$p_{g}(t) = \underbrace{\frac{\hat{V}_{1}}{2} \hat{I}_{1} \cos \phi_{1}}_{P_{g1}} + \underbrace{\frac{\hat{V}_{1}}{2} \hat{I}_{1} \cos(2\theta + \phi_{1})}_{\tilde{p}_{g1}(t)} + \underbrace{\hat{V}_{1} I_{DCg} \cos \theta}_{\tilde{p}_{0}}$$

$$p_{g}(t) = \underbrace{\frac{\hat{V}_{1}}{2} i_{d}}_{P_{g1}} + \underbrace{\frac{\hat{V}_{1}}{2} i_{d} \cos 2\theta - \frac{\hat{V}_{1}}{2} i_{q} \sin 2\theta}_{\tilde{p}_{g1}(t)} + \underbrace{\hat{V}_{1} I_{DCg} \cos \theta}_{\tilde{p}_{0}}$$

$$(3-10)$$

The instantaneous grid power comprises the average power  $P_{g1}$  and the oscillating power components  $\tilde{p}_{g1}(t)$  and  $\tilde{p}_{0}(t)$  resulting from the AC and DC components of the grid current. Disregarding losses in the LCL filter and VSC, the power equilibrium at the DC bus can be expressed as:

$$v_D(t) \left( C_D \frac{dv_D(t)}{dt} \right) = p_g(t) - P_D(t) \tag{3-11}$$

In this equation,  $P_D(t)$  represents the power output from the bus to the DAB

In this equation,  $P_D(t)$  represents the power output from the bus to the DAB DC-DC converter. It is assumed that  $v_D(t)$  is closely controlled to remain around the reference value  $V_D^*$  (Vule & Kuperman, 2022). Consequently, the linearization of (3-11) results in:

$$V_D^* \left( C_D \frac{dv_D(t)}{dt} \right) \approx p_g(t) - P_D(t)$$

(3-12)

The bus voltage  $v_D(t)$  comprises the average value  $V_D(t)$  and the ripple component  $\tilde{v}_D(t)$  expressed as:

$$v_D(t) = V_D(t) + \tilde{v}_D(t). \tag{3-13}$$

Therefore, replacing equations (3-10) and (3-13) into equation (3-12) yields the average and oscillating components as follows:

$$V_D^* C_D \frac{dV_D(t)}{dt} \cong \frac{\hat{V}_1}{2} i_d - P_D(t).$$

$$V_D^* C_D \frac{d\tilde{v}_D(t)}{dt} \cong \tilde{p}_{g1}(t) + \tilde{p}_0(t) .$$

(3-14)

It's important to note that the dynamics of the average bus voltage equation (3-14) hold true when the loop bandwidth is lower than the frequency of the oscillating components. The oscillating powers  $\tilde{p}_{g1}(t)$  and  $\tilde{p}_{0}(t)$  result in an approximation of the bus voltage ripple, given by:

$$\tilde{v}_{D}(t) \approx \frac{1}{V_{D}^{*}C_{D}} \int \left( \tilde{p}_{g1}(t) + \tilde{p}_{0}(t) \right) dt$$

$$\tilde{v}_{D}(t) \approx \underbrace{\frac{\hat{V}_{1}\hat{l}_{1}}{4\omega C_{D}V_{D}^{*}} \sin(2\theta + \phi_{1})}_{\tilde{v}_{D2\omega}} + \underbrace{\frac{\hat{V}_{1}I_{DC_{g}}}{\omega C_{D}V_{D}^{*}} \sin\theta}_{\tilde{v}_{D\omega}} \right).$$

(3-17)

The oscillating power component  $\tilde{p}_{g1}(t)$  induces the  $2\omega$  ripple component  $\tilde{v}_{D2\omega}(t)$ , while the  $\omega$  component  $\tilde{v}_{D\omega}(t)$  results from  $I_{g0}$ . Both of these ripple components traverse through the bus voltage control loop. Subsequently, the bus voltage controller  $G_{cv}(s)$  generates the reference current  $i_d^*(t)$  as:

$$i_{d}^{*}(t) = \hat{I}_{1} \cos \phi_{1} + \underbrace{\hat{I}_{rp2} \cos(2\theta + \psi_{2})}_{i_{d2\omega}^{*}(t)} + \underbrace{\hat{I}_{rp1} \cos(\theta + \psi_{1})}_{i_{d\omega}^{*}(t)}$$

(3-18)

The components of ripple  $\tilde{\iota}_{d\omega}^*(t)$  and  $\tilde{\iota}_{d2\omega}^*(t)$  in  $i_d^*(t)$  represent the residuals from the bus voltage regulator. The bus voltage control loop regulates the amplitudes  $\hat{l}_{rp2}$  and  $\hat{l}_{rp1}$ , as well as the phase angles  $\psi_2$  and  $\psi_1$ . The reference grid current is expressed as:

$$i_g^*(t) = i_d^*(t)\cos\theta + i_q^*(t)\sin\theta.$$

(3-19)

Replacing equation (3-18) into equation (3-19) yields:

$$i_{g}^{*}(t) = \underbrace{\hat{l}_{1} \cos \phi \cos \theta}_{Active \ power} - \underbrace{i_{q}^{*} \sin \theta}_{Reactive \ power} + \underbrace{\frac{\hat{l}_{rp2}}{2} \cos(\theta + \psi_{2})}_{Additional \ reactive \ power} + \underbrace{\frac{\hat{l}_{rp2}}{2} \cos(3\theta + \psi_{2})}_{Caused \ by \ l_{g0}} + \underbrace{\hat{l}_{rp1} \cos(2\theta + \psi_{1})}_{Caused \ by \ l_{g0}}.$$

(3-20)

The desired components of  $i_g^*(t)$  comprise the first two terms in equation (3-20). The  $2\omega$  ripple component generates the 3rd harmonic and additional reactive power components, typically mitigated by either a low-bandwidth bus voltage control loop (Karimi-Ghartemani et al., 2013) or a notch filter. The DC component  $I_{g0}$  of the grid current introduces the DC and 2nd harmonic components in  $i_g^*(t)$ . This DC component  $I_{g0}$  can be minimized through precise calibration of the grid measurement.

Suppression techniques involving additional circuits enable online adjustment of the DC component (Zhang et al., 2019).

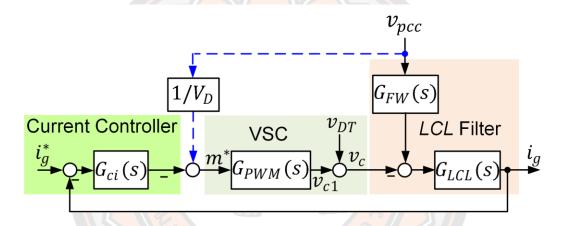

## **Analysis of Harmonic Mitigation Techniques**

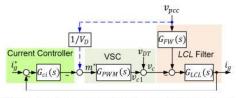

Harmonic Rejection Analysis of The Grid Current Control loop

Figure 17 illustrates the block diagram representing the grid current control in the stationary reference frame. The transfer functions of the LCL filter, denoted as  $G_{LCL}(s)$  and  $G_{FW}(s)$ ,

Figure 17 Block diagram depicting grid current control in the stationary reference frame.

are defined as:

$$G_{LCL}(t) = \frac{sC_f R_f + 1}{C_f L_1 L_2 s^3 + C_f (L_1 + L_2) R_f s^2 + C_f (L_1 + L_2) s}$$

(3-21)

$$G_{FW}(s) = \left(\frac{L_1 C_f s^2}{C_f R_f s + 1} + 1\right) \tag{3-22}$$

Here  $L_1$ ,  $L_2$ ,  $C_f$ , and  $R_f$  represent the parameters of the LCL filter. The ideal voltage  $v_{c1}(t)$  of the VSC is derived through pulse width modulation (PWM) using the modulation signal  $m^*$  from the output of the current controller. The PWM process is characterized by the following transfer function model:

$$G_{PWM}(s) = \frac{v_{c1}(s)}{m^*(s)} = V_D e^{-sT_d}$$

(3-23)

Here,  $T_d = 2T_s$  represents the delay time attributed to the sampling process and transport delay (Holmes et al., 2009), where  $T_s$  denotes the sampling period. The current controller  $G_{ci}(s)$  may take the form of a proportional-resonant (PR) regulator in the stationary reference frame or a proportional-integral (PI) regulator in the synchronous reference frame.

$$G_{ci}(s) = K_{p1} + \frac{K_{i1}s}{s^2 + \omega^2}$$

(3-24)

Here  $K_{p1}$  and  $K_{i1}$  denote the controller gains. The closed-loop transfer function of the grid current control is expressed as:

$$G_{cl}(s) = \frac{i_g(s)}{i_g^*(s)} = \frac{G_{cl}(s)G_{PWM}(s)G_{LCL}(s)}{1 + G_{cl}(s)G_{PWM}(s)G_{LCL}(s)}.$$

(3-25)

The current controller  $G_{ci}(s)$  in (3-24) in equation (3-24) exhibits an infinite gain at the grid frequency  $\omega$ , ensuring that  $|G_{cl}(j\omega)| \approx 1$ . However, the controller's finite gain at frequencies  $2\omega$  and  $3\omega$  still partially follows the  $2\omega$  and  $3\omega$  components of  $i_g^*(t)$  in equation (3-20). The admittances  $Y_{DT}(s)$  and  $Y_{pcc}(s)$  represent the influence of the dead-time and PCC voltages on the grid current, given by:

$$Y_{DT}(s) = \frac{i_g(s)}{v_{DT}(s)} = \frac{-G_{LCL}(s)}{1 + G_{ci}(s)G_{PWM}(s)G_{LCL}(s)}$$

(3-26)

$$Y_{pcc}(s) = \frac{i_g(s)}{v_{pcc}(s)} = \frac{G_{FW}(s)G_{LCL}(s)}{1 + G_{cl}(s)G_{PWM}(s)G_{LCL}(s)}.$$

(3-27)

Equations (3-26) and (3-27) show that  $G_{ci}(s)$  in equation (3-24) can only attenuate the fundamental components of  $v_{DT}(t)$  and  $v_{pcc}(t)$ . Optionally, incorporating a feedforward of the PCC voltage enhances dynamic performance and aids in mitigating PCC voltage harmonics (Somkun, 2021), expressed as:

$$Y_{pcc}(s) = \frac{i_g(s)}{v_{pcc}(s)} \approx \frac{(G_{FW}(s) - 1)G_{LcL}(s)}{1 + G_{ci}(s)G_{PWM}(s)G_{LCL}(s)} = \frac{\left(\frac{L_1C_f s^2}{C_f R_f s + 1}\right)G_{LcL}(s)}{1 + G_{ci}(s)G_{PWM}(s)G_{LCL}(s)}$$

(3-28)

## **Unified Harmonic Mitigation Structure**

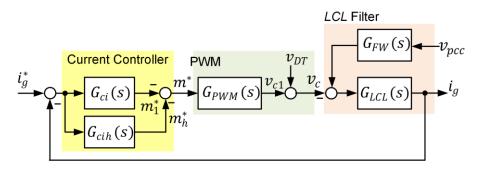

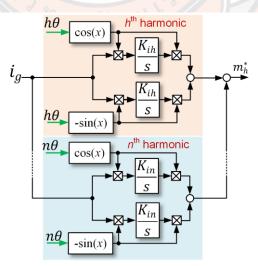

To address voltage harmonics, mitigation often involves employing a harmonic compensator (HC)  $G_{cih}(s)$ , the transfer function of which in the stationary reference frame is described as:

$$G_{cih}(s) = \sum_{h=3}^{n} \frac{K_{ih}s}{s^2 + (h\omega)^2}$$

(3-29)

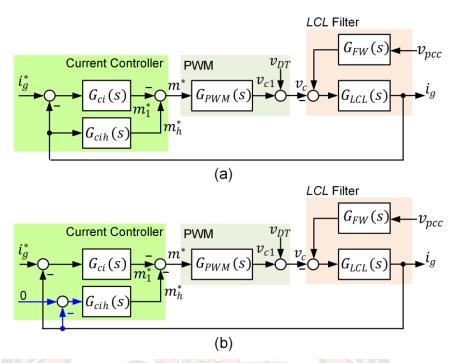

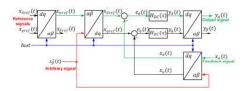

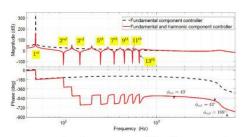

Here,  $K_{ih}$  represents the controller gain at the harmonic order h. The HC  $G_{cih}(s)$  can be implemented using PI controllers in the multiple-synchronous reference frame, proportional-multi-resonant (PMR) regulators, or repetitive controllers, all of which exhibit sufficiently large gains at the chosen frequencies. Figure 18 depicts the typical parallel structure of the grid current control with a harmonic controller in the stationary reference frame. The outputs  $m_1^*$  and  $m_h^*$  from the fundamental and harmonic controllers combine to form the modulation signal  $m^*$ . Equations (3-30) to (3-32) in Table 2 summarize the harmonic responses of this parallel structure. Equation (3-30) illustrates that this structure follows the harmonic components of the reference current  $i_g^*(t)$  at the selected frequencies due to the large gains of the HC. These large gains attenuate the harmonic components of the PCC and dead-time voltages, as shown in equations (3-31) and (3-32) (Somkun, 2021).

Table 1 Harmonic Rejection Characteristics of the Grid Current Control Structures

| Transfer functions                       | Parallel HC structure in Fig. 6                                                                             |        | Zero-reference HC structure in Fig. 7                                                  |        |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------|--------|

| $G_{cl}(s) = \frac{i_g(s)}{i_g^*(s)}$    | $\frac{\{G_{cl}(s) + G_{clh}(s)\}G_{PWM}(s)G_{LCL}(s)}{1 + \{G_{cl}(s) + G_{clh}(s)\}G_{PWM}(s)G_{LCL}(s)}$ | (3-30) | $\frac{G_{cl}(s)G_{PWM}(s)G_{LCL}(s)}{1+\{G_{cl}(s)+G_{clh}(s)\}G_{PWM}(s)G_{LCL}(s)}$ | (3-33) |

| $Y_{DT}(s) = \frac{i_g(s)}{v_{DT}(s)}$   | $\frac{-G_{LCL}(s)}{1 + \{G_{ci}(s) + G_{cih}(s)\}G_{PWM}(s)G_{LCL}(s)}$                                    | (3-31) | $\frac{-G_{LCL}(s)}{1 + \{G_{ci}(s) + G_{cih}(s)\}G_{PWM}(s)G_{LCL}(s)}$               | (3-34) |

| $Y_{pcc}(s) = \frac{i_g(s)}{v_{pcc}(s)}$ | $\frac{G_{FW}(s)G_{LCL}(s)}{1 + \{G_{ci}(s) + G_{cih}(s)\}G_{PWM}(s)G_{LCL}(s)}$                            | (3-32) | $\frac{G_{FW}(s)G_{LCL}(s)}{1 + \{G_{cl}(s) + G_{clh}(s)\}G_{PWM}(s)G_{LCL}(s)}$       | (3-35) |

Figure 18 Grid current control with parallel HC scheme.

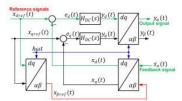

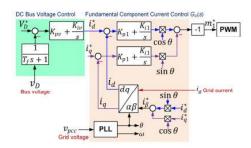

Figure 19(a) illustrates an alternative grid current control structure, which is equivalent to Figure 19(b) when the reference signal for the selective harmonic controller is set to zero. The transfer functions of this zero-reference HC structure are outlined in equations (3-33) to (3-35) in Table 2. The substantial gains of the HC at the selected frequencies simultaneously dampen the harmonic components in  $i_g^*(t)$ ,  $v_{DT}(t)$ , and  $v_{pcc}(t)$ . Additionally, both the parallel and zero-reference HC schemes exhibit identical suppression characteristics of the dead-time and PCC voltages, as indicated in equations (3-31) and (3-34), as well as equations (3-32) and (3-35). Consequently, the zero-reference HC scheme enhances the bandwidth of the conventional bus voltage control, thereby improving dynamic response and reducing bus capacitance without constraining grid current distortion. In contrast, existing bus voltage control schemes have primarily focused on generating a clean reference for the grid current control loop.

Figure 19 Grid current control proposal featuring a zero-reference HC scheme.

# **Proposed VSC Control scheme**

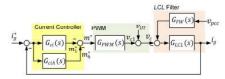

Unbalanced synchronous reference frame control

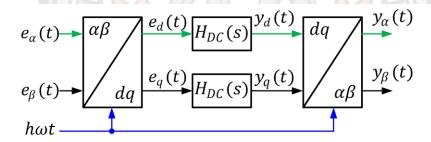

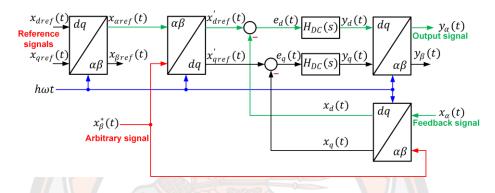

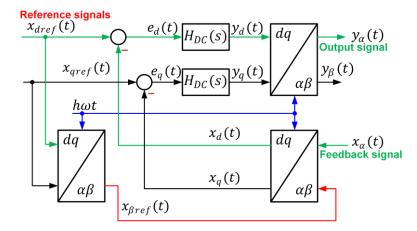

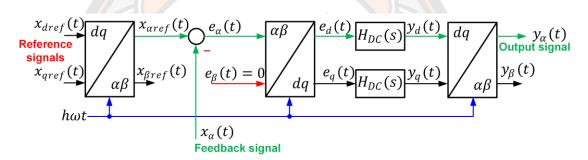

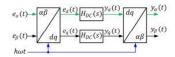

The unbalanced synchronous reference frame control (Somkun & Chunkag, 2016b) is adopted for controlling both the fundamental and harmonic components of the current. Figure 20 illustrates the stationary frame representation of the transfer function  $H_{DC}(s)$  implemented on the synchronous reference frame at  $h\omega t$  (Monfared et al., 2014). The error signals in the stationary reference frame  $e_{\alpha}(t)$  and  $e_{\beta}(t)$  are derived from:

$$\begin{bmatrix} e_{\alpha}(t) \\ e_{\beta}(t) \end{bmatrix} = \begin{bmatrix} x_{\alpha ref}(t) \\ x_{\beta ref}(t) \end{bmatrix} - \begin{bmatrix} x_{\alpha}(t) \\ x_{\beta}(t) \end{bmatrix}$$

(3-36)

Here  $x_{\alpha}(t)$  and  $x_{\beta}(t)$  represent the controlled signals, while  $x_{\alpha ref}(t)$  and  $x_{\beta ref}(t)$  denote the reference signals in the  $\alpha\beta$  -axes. The error signals  $e_{\alpha}(t)$  and  $e_{\beta}(t)$  are converted to the error signals  $e_{\alpha}(t)$  and  $e_{q}(t)$  in the synchronous reference frame using the Park transformation: